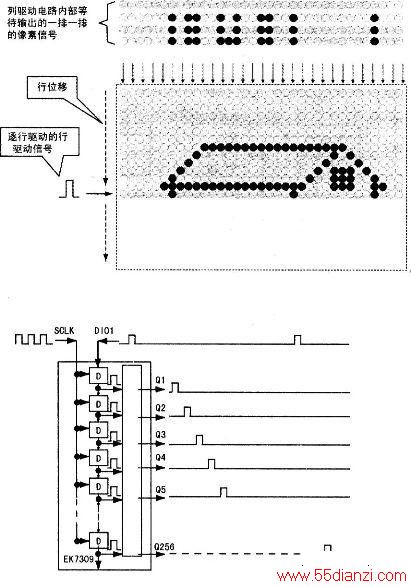

行驱动电路需要的信号

DIO1/DIO2:行位移起始控制信号;CLK:行位移时钟信号等。这些信号控制行驱动电路产生由屏上方逐步向下扫描的逐行驱动电极线的驱动信号,把列驱动电路送来的像素信号逐行排列,由上向下扫描一次,显示一幅图像,如上图所示。

1.行驱动电路

工作原理如下图所示,行驱动电路实际是一个由D触发器组成的双向位移寄存器,下面以EK7309为例介绍行驱动电路。

从下图中可以看出,SCLK行频时钟信号进入集成电路后加到每一个D触发器上,D101行位移起始控制信号加到第一个触发器的输入端;第一个D触发器的输出信号在输出(Q1输出)的同时又进入第二个D触发器的输入端,DIO1是由第一个触发器输入在SCLK的控制下逐个后移,以此类推。

由此可以看出液晶屏的行驱动电路就是起到类似CRT显示的场扫描作用一样。

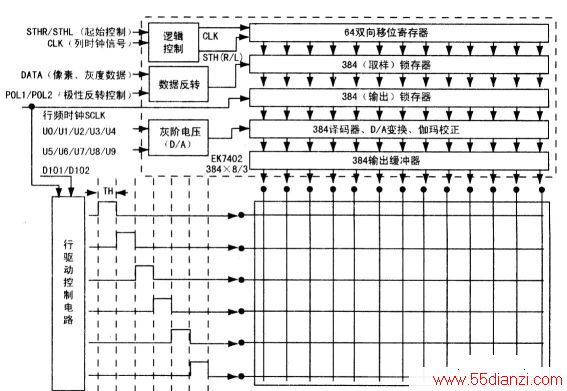

2.列驱动电路工作原理

液晶屏列驱动电路的结构、工作原理比行驱动电路复杂得多。最终加到液晶屏列驱动电极线上的信号。是以一行像素为一排(并行)的模拟信号,它以一行时间为单位同时加到列电极线上。时序转换电路按照列驱动电路和行驱动电路的要求,对前端电路送来的图像视频信号(LVDS)进行重新排列、组合、变换,并向列驱动电路提供DATA、STHR/STHL、CLK、POL1/POL2等一系列控制信号。列驱动电路把这些控制信号再转换为一排一排的像素、并行排列的模拟信号加到列电极线上。这一过程是在一块专门的列驱动集成电路内来完成的。典型的列驱动集成电路型号是:EK7402,图7显示的就是EK7402的内部框图。下图中显示了由时序转换电路送来的DATA、STHR/STHL、CLK、POL1/POL2信号转换成液晶屏驱动信号的过程。下面介绍列驱动电路工作原理及屏信号形成的过程。

列驱动电路主要由64位双向移位寄存器、384取样锁存器、384输出锁存器、384译码器、384输出缓冲器等几个主要电路组成。

(1)64位双向移位寄存器 输入STHR信号及CLK信号。在64位双向移位寄存器中,STHR信号在CLK信号的控制下输出对图像数据信号DATA进行一行取样的取样信号,如下图所示。

(2)384取样锁存器64位双向移位寄存器送来的取样信号在这个384取样锁存器中对DATA图像像素数据信号(R、G、B)进行一行取样,成为并行的一行像素信号,并进行存储。384表示这块集成电路中可以进行384路信号取样。

(3)384输出锁存器取样锁存器取样的一排一排信号存储在384输出锁存器中。输出锁存器在行驱动电路送来的行时钟信号SCLK控制下,一行一排、一行一排地输出像素信号。一排信号的输出由一个SCLK(STB)信号的上升沿控制。

(4)384译码器实际上是一个把数字信号转变为模拟信号(D/A)的转换电路,因为液晶屏最终是控制亮度的强弱产生图像,其驱动信号必须是模拟信号。

(5)384输出缓冲器 对输出信号幅度进行放大和实现液晶屏的阻抗匹配。

列驱动电路除了以上5个主要的信号处理电路外,还有几个配合上述电路完成信号处理的辅助电路。这些电路是:逻辑控制、数据反转、灰阶电压及伽玛校正电路。

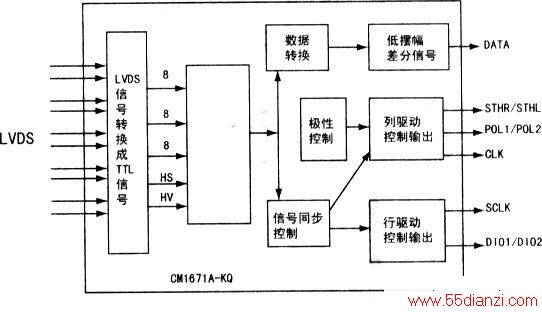

上图所示是集成电路内部框图。从图9可以看出:电视机图像处理电路送来的五对LVDS差分信号(TX0、TX1、TX2、TX3、TX4、TXCLK)进入集成电路内部后,先还原成8位数字信号,然后通过数据信号的重新组合形成行、列驱动集成电路所需要的DATA、STHR/STHL、CLK、POL1/POL2DIO1/DIO2、CLK信号加到列、行驱动集成电路上。

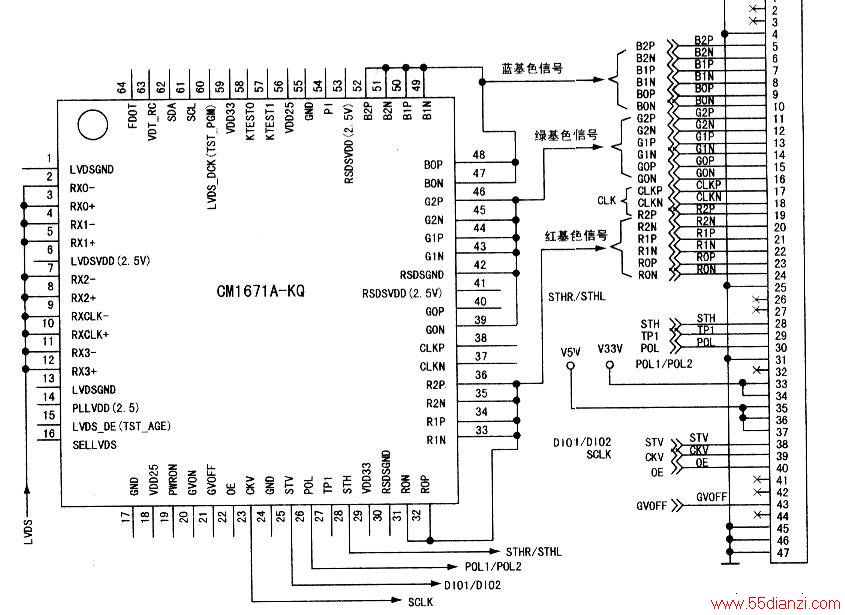

下图所示是CM1671A-KQ应用电路图,主要为输入信号和输出信号路径图,可以用示波器、数字电压表来判断故障所在。

CM1671A-KQ各引脚功能及实测数据见表。