��������

����Super-junction���͵ĸ�ѹ����MOSFET���и��͵ĵ�ͨ���裬�����ͨ�ŵ�Դ����������Դ����Դ�������Լ�̨ʽ���Ե�Դ��������������Ӧ���еõ��㷺��ʹ�á�Alpha MOS���ǻ���Super-junction���������ĸ�ѹ����MOSFET�������8Ӣ�羧Բ�������������������ܺͿɿ��ԡ�

����������Ҫ���Alpha MOS��������������У����·(PFC)�е����Ҫ���ע�������������ͽ��������

����1.Alpha MOS��������

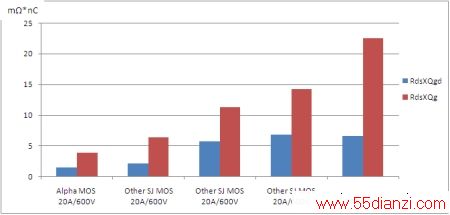

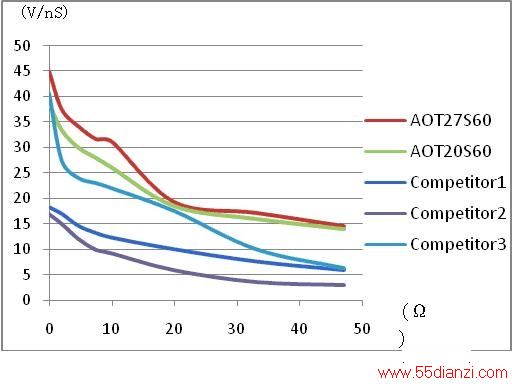

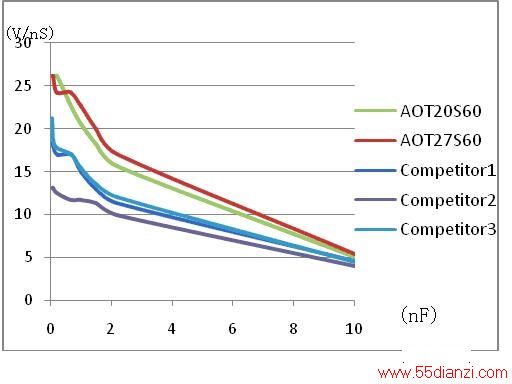

����Alpha MOS�ĵ�ͨ����xоƬ���(RdsA)����ָ���AOSƽ�湤��MOSFET��3.5������ͨ����x���յ���(RdsxQgd)���ܱ�ƽ�湤��MOSFET��5.7����Alpha MOS��Ŀǰsuper-junction��Ʒ��ͬ�ȼ���FOM������ߵģ���ͬ�ȼ������ڶ��ĸ��ٿ�����super-junction ��Ʒ�߳�45%(ͼ1)��

ͼ1��RdsxQgd��FOM(RdsxQg)�����ܶԱ�

��������Alpha MOS ���п����ٶȿ죬�����С���ص㣬�Լ��ٿ�����ģ����Ч���кܴ�������������������Ҫ������С�ġ��봫ͳ��MOSFET��ȣ�Alpha MOS��Ҫ����ϸ�����������·��PCB���ߣ��ڲ���Ӧ����Ҳ��Ҫ����ע��������������źŵ�Ӱ�졣

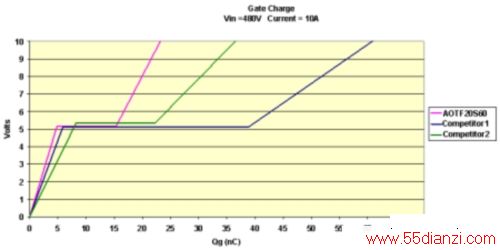

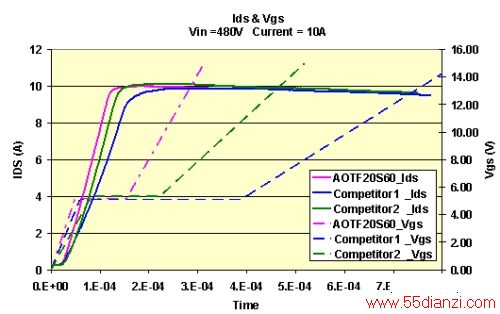

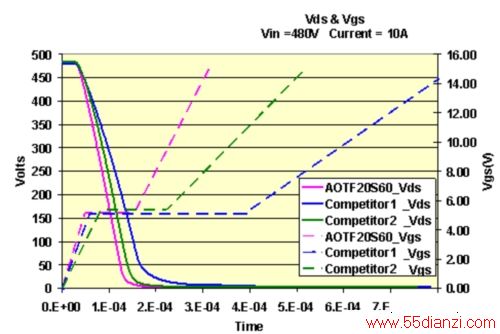

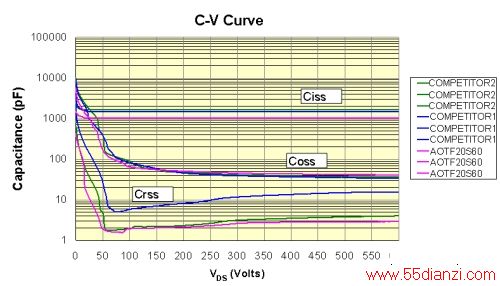

����Super-junction���͵�MOSFET���������еĿռ��ɽṹ�������ٶȱȴ�ͳMOSFET��Ķࡣͼ2-ͼ5��600V/20A�ȼ�super-junction ��Ʒ�Ŀ������ԶԱȡ�competitor1Ϊ��Դ���ƷӦ����㷺��һ��super-junction�� MOSFET��competitor2������һ�ָ��ٿ����͵�super-junction MOSFET��

ͼ2���ż�������ɶԱ�

ͼ3��©���������ż�������ϵ�Ա�

ͼ4��©����ѹ���ż�������ϵ�Ա�

ͼ5���������©����ѹ��ϵ�Ա�

�����ӶԱ��п��Կ���Alpha MOS��Ҫ�������ڽ���ݣ�ͬ�ȼ���MOSFET�����ԽС����ͬ�����������¿����ٶȾ�Խ�죬��Ӳ���ص�·�У�����һ���ܴ�����ơ����ǹ���Ŀ����ٶȻ�����ܸߵ�dv/dt��di/dt�������MOS�Ĺ����ɿ������к��ģ�ͬʱҲ�ǵ�Դϵͳ����������Դ��

����Alpha MOS��Qg��С�����ڼ�����������Ǹ��ŵ㡣��ʵ��Ӧ���У�Qg����CissС��MOSFET�����������źŸ������������ʻ�·�ĸ��ţ��ر��ڸ�ѹӦ�����������ʮ��ͻ��������Կ����ٶȲ������ƣ����ߵ�dv/dt ��������ϵ�������·�У���������ź����ң���������MOS�ջ١�

�����ڴ���Ӧ���У�MOS�IJ��������dz��õ��ֶΡ����Ƕ�����Alpha MOS�����ĸ��ٿ���������������Ҫ����ע�⡣�����ٶ�Խ���MOS������ʱԽ�����¹�����ƽ�⣬��������ѡ�������ᵼ�¶���ĸ��š�

�������Կ�����Alpha MOS��Ȼ�������쵫�Ƕ����ʹ�õ�Ҫ��Ҳ�Ƚϸߡ��������紫ͳ�Ŀ�����������“��������”��ѡ����ʵ����ˣ���ϸ�������������������滮PCB���֣������������ӵ�·���ȶ��ԣ����ⲻ��Ҫ���ظ��Ͷ���

����2��Alpha MOS������·���

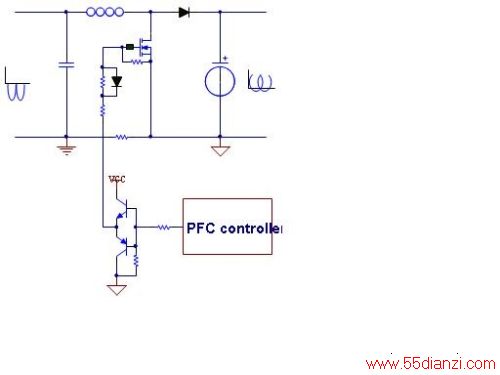

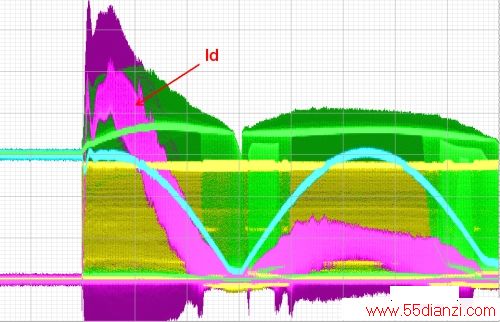

����PFC�ǵ�Դ�����ж�MOSҪ��Ƚϸߵ�����֮һ��������Ϊ����1��PFC�бȽϿ��������ѹ��Χ���ִ���Դ��Ҫ����90-264V��ȫ��Χ������ѹ�¹���������ζ��MOS��Ҫ���㹻����ѹ�ȼ���Ҫ�ܳ��ܽϴ��������2��PFC�Ŀ��ƻ�·�ٶȱȽ�����Ϊ��ƽ��100Hz/120Hz�Ľ��������Ʋ���PFC��Ӧʱ�����ﵽ��ʮms��������Ƶ�·��ICû��ר�Ž����Ż���������������������ܴ�ij����������������ɴ���������ʱ��5-10������3����ȱ��Ƿѹ������PFC�У���������ѹ��������90V�ܶ�ʱ����·���п��ܼ�����������Ҳ������ܸߵĿ��ط�ֵ���������¸��ź�Ӧ������������Χ��ͼ6Ϊ���͵�PFC��·��ͼ7ΪPFC����ʱ��MOSFET©���ij������ʾ��ͼ��

ͼ6�����͵�PFC��·

ͼ7��PFC������MOSFET©���ij������

MOSFET��������·�Ѿ��кܶ����ķ�������ʵ��Ӧ���У����ڳɱ����ǣ��ܶ�������·���� �ñȽϼ�оƬֱ�������������ڴ��ʺ�����Ҫ��Ƚϸߵ�Ӧ���У�������·����ƶ�MOSFET�Ŀɿ��Ժ�ϵͳ���������кܴ�Ӱ�졣

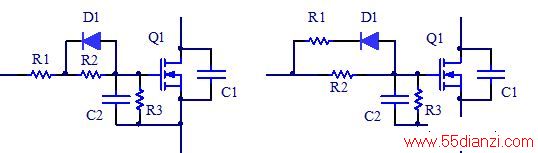

ͼ8:MOSFET���ֻ���������·�ṹ

������ͼ8���������MOSFET������·��R1��R2��Rg����ͼR1+R2��������ѹ����ʱ�ij����裬R1������Ϊ�ŵ���裬��ͼR2������Ϊ�����裬R1��R2������Ϊ�ŵ���衣R3�������Էŵ���衣C1��C2�ֱ�����ӵ�Cds��Cgs���ݡ�

������1��dv/dt�Ŀ��Ʋ��Ժ�ע������

����Ӱ��dv/dt��������MOS�������ԡ�����ʱ�ĵ�����ֵ���Լ�������·��Rg�ȡ�����Alpha MOS��Ciss�ر�С���ʵ�������CgsҲ����Ч����dv/dt�ķ�����

������ȻMOSFET�����ɳ��ܵ�dv/dt��di/dt�ܸߣ����Ǹ��ݾ������ݱ�����ͨ���ı�Rg��Cgs������dv/dt������20V/ns����Ӧ��di/dt������200A/ns����ʵ�ʵ�·�����нϺõĹ���״̬����Ч������������£�dv/dtС��10V/ns��di/dtС��100A/ns�������ڿɿ��ԣ���ͼ9��ͼ10��ʾ��

����PFCӦ���д��ڿ������ѹ��Χ�������ѹ���䣬�Լ���Ӧʱ�������ص㣬���׳��ֱȽϴ�ij��������������Ӧ������Ҫ�ر�ע����Ʒ�ֵ������ͬ�������������£���ֵ����Խ���ص�dv/dt��di/dtԽ��Ҫ����ʵ��Ӧ���е�����ֵ��������������������������У�Ҫ�������������µĿ��ز��Σ���ȷ���Ƿ���Ҫ��������������ʹMOSFET�����ڽϺõ�״̬��

����ͨ��©Դ�����Ӷ���ĵ���Ҳ���ԱȽ����ؼ�Сdv/dt����������Դ��λ����ʽ�����أ�г�����·�У����ʵ�©Դ�����������ڿ���״̬���Ż�������PFC�ͷ������·������ҪС�Ĵ�����Ҫ��Ч�ʽ����ʵ���ƽ�⡣��Ч�������ķ�Χ�ڣ�ͨ������©Դ�����ݻ�������Ч�ؼ���EMI��

ͼ9��MOSFET�ض�dv/dt��ŵ�����ϵ

ͼ10��MOSFET�ض�dv/dt��Cgs��ϵ

��2������ͨ��Cgd��϶������ĸ���

���Ĺؼ��֣�У�� ����������������Դ�������� - ������������