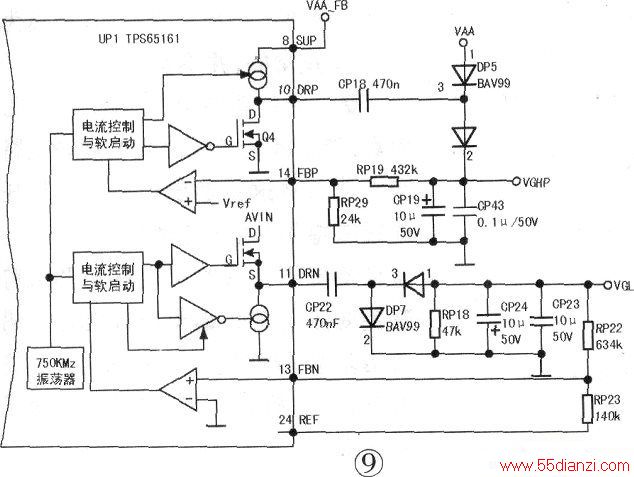

VGH、VGL电压产生电路由UP1的8、10、14、11、13、24脚内部电路与外围电路构成,如图9所示。

逻辑板上的主芯片输出PWR-ON信号到UP1的⑨脚(EN2),在26脚内外电路延时作用下,⑧脚输入电压VAA-FB经UP1内部电流控制与软启动电路控制后分别从UP1的10、11、8脚输出脉冲,下面分别讨论。

(1)VGL电压产生电路(分两个时段讨论)

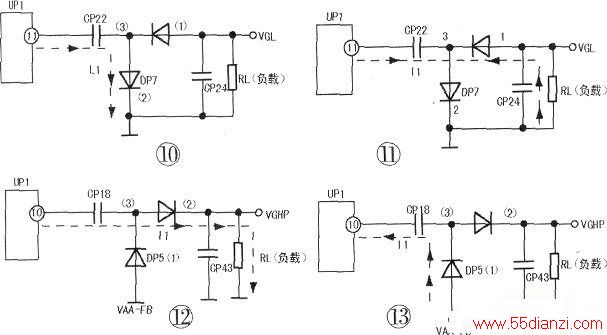

1)t0~t1时段,在这个时段内,UP1(11)脚输出正极性的脉冲,经CP22耦合至DP7的(3)处(如图10所示),由于这个时段是正极性脉冲,DP7(3)~(1)处的二极管处于反向偏置而截止,而DP7(3)、(2)处的二极管处于正向偏置而导通,UP1的(11)脚输出的正极性脉冲经CP22、DP7(3)~(2)二极管构成回路,并对CP22充电,电流方向如图10中L1所示。

2)t1~t2时段,在这个时段内,UP1的(11)脚输出负极性的脉冲(可参考图4,只是脉冲幅度及占空比不同),DP7(3)~(2)处的二极管反偏而截止,而DP7(3)~(1)处的二极管正偏导通,负极性的脉冲经DP7(3)~(1)处的二极管整流.CP24滤波而得到VGL负电压,如图11中的12所示。

为了稳定输出电压,UP1(24)脚输出基准电压经RP23送至UP1(13)脚,输出电压经RP22取样也送UP1(13)脚,经内部电路处理后,控制输出脉冲的占空比,实现稳压(如图9所示),重复以上周期可得到稳定持续的VGL电压。

(2)VGH电压产生电路(分两个时段讨论)

1)t0~t1时段,在这个时段内,UP1⑩脚输出正极性的脉冲(可参考图4,只是脉冲幅度及占空比不同),经CP18耦合,DP5(3)~(2)二极管整流.CP43、CP19滤波,可得到5V左右的电压,如图12所示。

2)tl-t2时段,在这个时段内,UP1的⑩脚输出负极性的脉冲,经CP18耦合到DP5(3)处,DP(3)~(2)处二极管反偏截止,DP5(3)-(1)处二极管正偏导通,VAA-FB电压经DP(3)~(1)处二极管,CP18与UP1的⑩脚构成回路,并对CP18充电,如图13所示。

重复以上周期,可得到持续稳定的VGH电压。

由于VGH电压较高,达到25~30V,用VAA-FB(20V)左右的电压经DP5(1)~(3)处二极管后,与DP5(3)~(2)处二极管整流滤波后得到的电压叠加,即可得VGHP电压,如图12所示。

为了稳定输出电压,VGHP电压经RP19、RP29分压后,反馈至UP1的14脚内部运放的反相输入端,与运放的正相输入端的参考电压比较后,送电流控制电路处理控制输出脉冲的占空比,从而实现稳压。

VGHP电压在主芯片输出的GVON和GVOFF信号作用下,控制QP7的导通与截止,经QP8稳压产生VGH电压,如图14所示。

本文关键字:液晶屏 显示电路-显示屏,单元电路 - 显示电路-显示屏