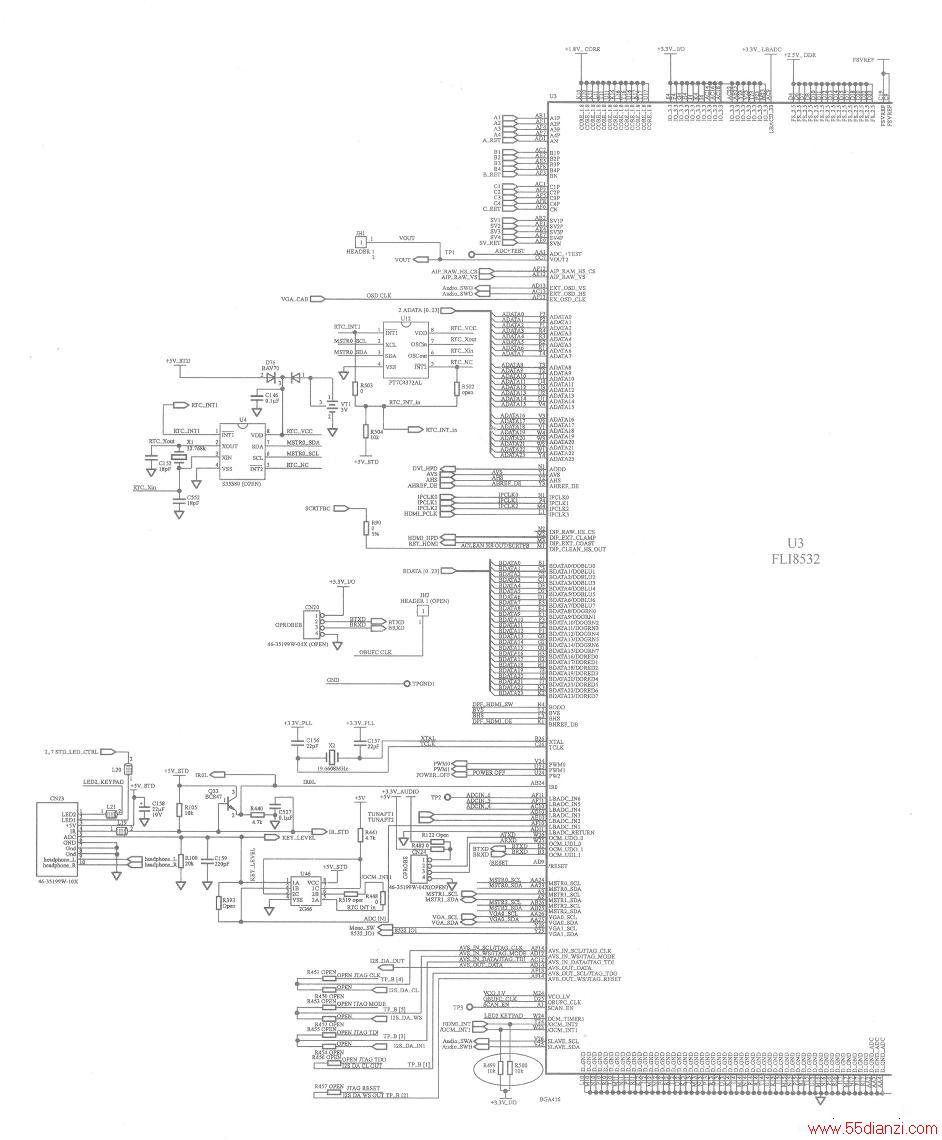

视频控制与处理电路以全功能超级芯片U3(FLI8532)为核心构成,有关电路如下图所示。

FLI8532是专门为液晶彩电和数字CRT彩电设计的全功能超级芯片,它具有带DCDi的3D数字图像解码器,具有图像质量增强、降噪等效果。模拟信号前端和VBI处理器使FLI8532能够适应全球化的TV产品设计;自动检测和不规范格式转换技术使FLI8532可以检测、处理和增强全球的任何视频格式或PC格式图像,而无需附加任何硬件电路;另外,FLI8532还包含嵌入式的微控制器和多功能的OSD电路,只需外接少量元器件,即可构成一台完整的液晶彩电。FLI8532内部电路框图及其有关介绍参见本书第三章相关内容。

电路的工作过程如下:

高频板副高频头输出的视频信号经R29限流后,由C43耦合到U3的AE7脚。

AV输入接口输出的AVl-V、AV2-V,AV3-V视频信号除送到U23(SAA71117AH)外,还有一路经Rl、R14、R18限流后,由C9、C20、C31耦合到U3的AB1、AF1、AC1脚。

S端子输出的Y/C信号除送到U23外,还送到U3。其中,Y信号经R28限流后,由C39耦合到U3的AE1脚;C信号经R24限流后,由C38耦合到U3的AE4脚。

YPbPr接口输出的Y、U、V信号分别经R7、Rll、R12限流后,由Cl0、C14、C15耦合到U3的AE5、AF5、AB2脚。

VGA接口输出的R、G、B信号分别经R55、R53、R46限流后,由C65、C64、C61耦合到U3的AF7、AF8、AE8脚。VGA接口的行、场信号分别经R69、R72耦合到U3的AF12、AE12脚。

由视频解码电路U23输出的数字视频信号输入到U3的BDATA[O:231输入端。另外,由DVI/HDMI解码电路U26(Si19021)输出的数字视频信号也输入到U3的BDATA[O:23]输入端。

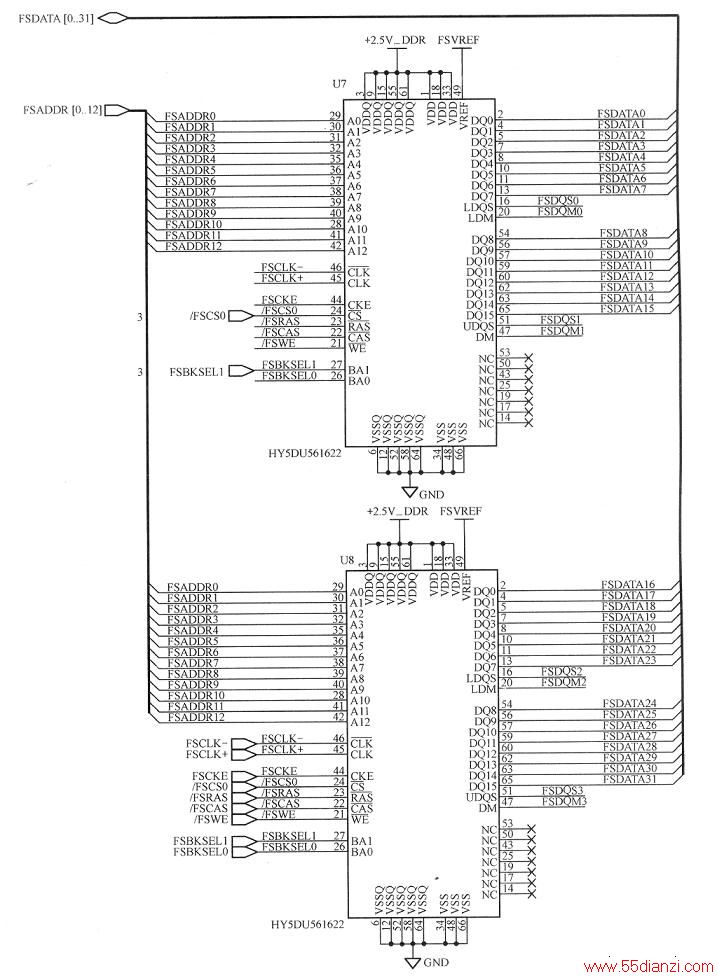

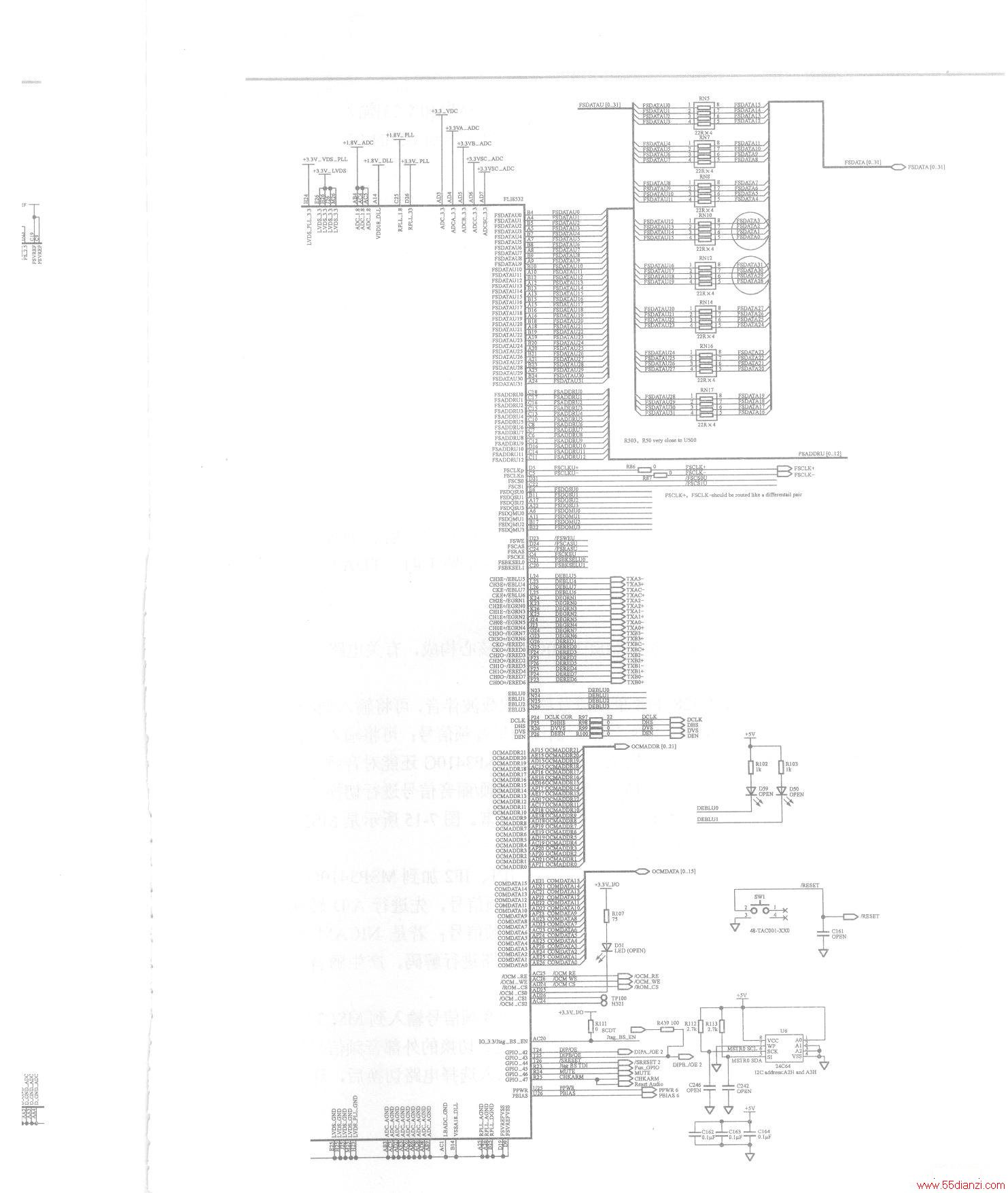

以上几种信号输入到U3内部电路后,首先由内部选择开关进行切换,送到A/D转换器,将模拟信号转换为数字信号。在外部帧存储器U7、U8(有关电路如上图所示)的配合下,U3对视频信号进行同步信号处理、VBI限幅、斜线角度处理、降噪、逐行变换、图像缩放变换、画质增强等处理,并生成主画面图像和子画面图像。然后,U3对2个画面的图像信号进行图像覆盖处理、1,校正、LCD加速驱动、OSD显示覆盖处理,最后,经U3内部的LVDS发送器处理后,输出8位双路串行数据和时钟。其中,8位奇路LVDS数据和时钟信号为:TXAO+.TXAO-,TXAl+.TXAl-,TXA2+、TXA2-,TXA3+、TXA3-,TXAC+、TXAC-;8位偶路LVDS数据和时钟信号为:TXBO+、TXBO-,TXBl+、TXBl-,TXB2+、TXB2-,TXB3+、TXB3-、TXBC+、TXBC-。奇路和偶路数据和时钟信号经连接电缆输出到液晶面板输入接口,驱动液晶屏显示出图像。

本文关键字:暂无联系方式电视机单元电路,单元电路 - 电视机单元电路