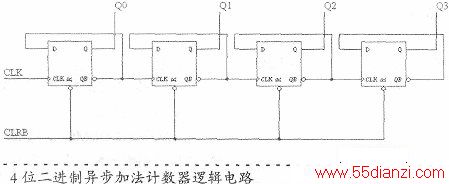

在上图的4位二进制异步加法计数器逻辑电路中,后一级触发器的CLK是连到前一级触发器的QB端。如果我们将后一级触发器的CLK是连到前一级触发器的Q端,就构成了4位二进制异步减法计数器,这些具体的设计实验可由读者完成。

3).10进制(任意进制)同步加法计数器简介 表为10进制同步加法计数器真值表,根据该表,我们可以取某个中间值(Q3—Q0=1010)来控制输出端清零,例如:在前9个脉冲时,计数器作加法输出;当第10个脉冲到来时控制计数器清零。利用这种方法,我们也可以设计出任意进制的计数器。

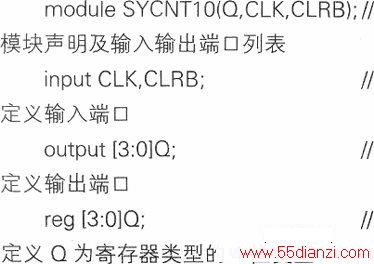

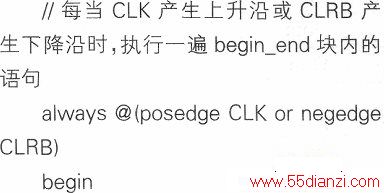

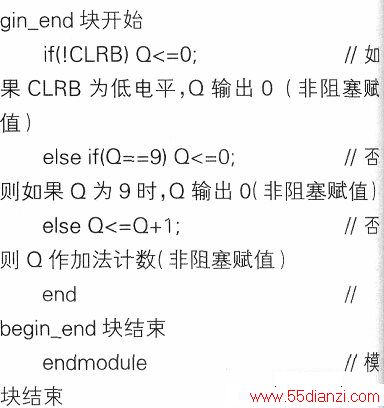

4).10进制同步加法计数器的设计在D盘中先建立一个文件名为SYCNT10的文件夹,然后建立一个SYCNT10的新项目,输入以下的源代码并保存为SYC-NT10.V。

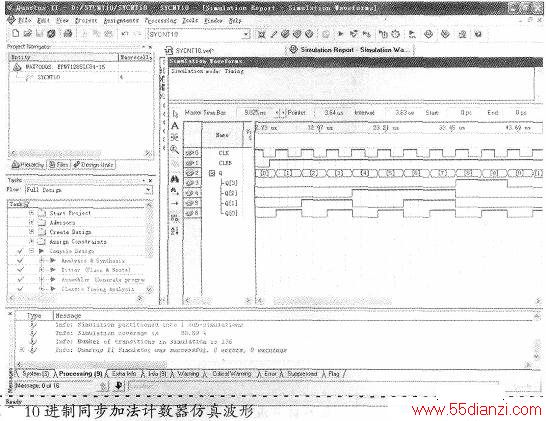

源代码输入完成后,我们将器件选择为EPM7128SLC84-15。引脚分配需要参考MCU&CPLDDEMO试验板的电路原理,这里的引脚分配见表loo器件编译通过后,可进行仿真,仿真终止时间(EndTime)设为100μs,时钟信号(CLK)半周期设为2μs,复位信号(CLRB)前5μs为低电平,之后为高电平。下图为10进制同步加法计数器在QuartusII集成开发软件中的仿真波形。接下来进行*.pof至*.jed的文件转换,最后将*.jed文件下载到ATF1508AS芯片中。

在MCU&CPLDDEMO试验板上,按动GCLK2键,可以看到,LEDO—LED3de输出状态从O变化到9,然后回到0。输出状态符合10进制同步加法计数器真值表(下表)。

10精致同步加法计数器真值表

10进制同步加法计数器引脚分配表

本文关键字:暂无联系方式综合-其它,电子制作 - 综合-其它