频谱分析仪按实现方式可分为模拟式和数字式两种,前者以模拟滤波器为基础,后者则以数字滤波器和FFT分析为基础。相比之下,模拟式频谱分析仪不能获得实时频谱,且由于模拟滤波器会受到非线性、温漂、老化等影响,测量精度不高; 而数字式频谱分析仪由于其基于数字滤波器,故而形状因子小,频率分辨率高,稳定性好,可以获得很窄的分析带宽,而测量精度较高; 而且由于它基于高速ADC技术、数字信号处理技术、FFT分析等进行设计,因而具有多种谱分析能力。随着现场可编程门阵列(FPGA) 器件、DSP器件等在芯片逻辑规模和处理速度等方面性能的迅速提高,数字式频谱仪的测量速度更快、实时性也更强。

在数字中频式频谱仪中,分辨率带宽滤波是数字中频处理模块设计的关键,它决定了频谱分析的有效信号带宽,同时表征频谱仪在响应中明确分离出两个输入信号的能力,是频谱仪的主要技术指标之一。为了满足信号的实时性和精度要求,通常以高速A/D采样得到数字中频信号,但其数据率过高,故其成为数字处理的瓶颈。一般需要使用数字正交解调技术将信号搬移至基带,然后通过多速率信号处理技术来设计抽取滤波器,以降低数据率,最终实现数字FIR滤波器。

本文采用数字下变频技术,并基于FPGA硬件设计数字中频处理模块,调用不同的IP核进行设计,同时采用参数可配置的结构来实现可变抽取率滤波器和分辨率带宽数字滤波器。由于IP核是经过了严格的性能测试并且进行了优化,时序稳定,因而可以满足系统高速与实时性处理的要求。

1 数字下变频原理

全数字中频处理技术是软件无线电中的关键技术之一,它主要应用于将中频信号下变频至基带信号,在降低采样率的同时,该技术可保证所需要的信号不被混叠,因而十分方便于后续更多基带信号处理技术的使用。全数字中频技术包含数字正交解调技术和多抽样率信号处理技术两部分。

1.1 数字正交解调

正交解调也称为正交变频,它主要通过数字混频实现,设输入中频信号为:

其中,信号中心频率远大于信号带宽B,且信号的采样速率满足奈奎斯特定理,即f0>>B,fs>2B。那么,经过正交变换后,该信号的基带调制信号为:

式中,ZBI (t) 称为I信号,ZBQI (t) 称为Q信号。由式(2) 可以看出,基带信号ZBI (t)、ZBQI(t)只包含振幅和相位信息且频率为零,因此,正交解调过程就是从中频信号x (t) 获得基带信号的过程。

正交解调过程的系统模块为正交双通道结构,分别称为I通道和Q通道。由于输入和正交本振、混频器均由数字实现,故具有集成度高、一致性好的特点,可以获得很好的通道一致性,而采用数控振荡器也使得相位的正交性也得到很好的保证。

1.2 多抽样率信号处理

由于对中频信号的采样率较高,而基带信号处理一般只需在较低的采样率下进行,因此,经数字正交解调后的基带信号都处于严重的过采样状态,必须进行采样率之间的转换,以降低数据流速率,这种信号采样率的变化就是基于多速率信号处理技术。

整数倍的抽取可使信号采样率降低整数倍,其抽取倍数为D。由于抽取降低了信号的采样率,所以,抽取后的信号可能不再满足奈奎斯特采样条件而产生混叠。而为了保证所需信号不失真,抽取前,一般先用数字低通滤波器根据抽取后的采样率对信号进行带限处理,以使滤波器的截止频率ωc为所需要信号的最大带宽B,当抽取前采样率fs1与抽取后采样率fs2满足fs2=fs1/D≥2B时,信号抽取后就不会产生混叠。

1.3 频谱仪多抽取率滤波器原理

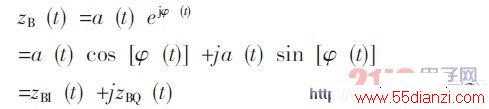

数字中频式频谱分析仪的分辨率带宽是通过多抽样率滤波器设计实现的。针对下变频后依然过采样的数据流,则需要以不同速率的滤波和抽取,以获得不同的实时分析带宽。这样,实际的抽取率变化范围很大,例如,当需要较窄的分辨率带宽时,其抽取率很高,要求采用多级的滤波和抽取来逐步降低采样率,这样也降低了对每一级抗混叠滤波器的要求。由于ADC是在中频进行采样,数据率和采样率是一致的,而FIR滤波器无法保证高采样率低带宽的设计,因此,要先通过CIC (梳状滤波器) 和HB (半带滤波器) 滤波抽取器进行大的抽取,使数据率快速降下来,再由FIR滤波器进行滤波。结合正交解调,数字下变频的结构框图如图1所示。

图1 数字下变频器结构框图

CIC (梳状) 滤波器的系数都为1,而且只有加法运算,没有乘法运算,因而硬件实现非常容易,同时可以达到很高的处理速率,很适合作抽取系统中第一级抽取和进行大的抽取因子。但单级CIC滤波器的过渡带和阻带衰减特性不好,通常需要采用多级级联方式来加大滤波器旁瓣电平衰减。选用5级级联时,阻带衰减约为67.3dB,可以满足第一级滤波器衰减要求。虽然CIC抽取率较高,但其频率响应3dB有效带宽很窄。而要保证有效带宽基本不变,且继续降低抽取率,其后级可以采用半带滤波器。

HB (半带) 滤波器的系数几乎一半为零,其滤波时的运算量可减少一半。而其抽取因子固定为2,因此,经过N级HB滤波器后,可以使采样率降低2N倍。多级滤波抽取后的频率响应在通带内无交叠,它只在过渡带边缘有交集,因而具有很好的抗混叠效果。

通过CIC和HB多组滤波器的滤波抽取,基带信号被降到了较低的采样率,可以适于FIR处理。

由于FIR滤波器的阶数较高,可以设计成过渡带小、阻带衰减高且具有很好波形因子的频率响应,以满足频谱分析仪对分辨率带宽滤波器的特别要求。

www.55dianzi.com

2 数字中频处理逻辑

近年来,FPGA器件在工艺及逻辑规模方面的快速发展和成本的不断降低,利用FPGA器件来实现高速专业数字下变频模块已经成为系统设计中的常用方法。FPGA芯片中不仅集成了大量的可编程逻辑资源,还包含了丰富的数字信号处理的硬核和固核资源,故能满足多种系统的数字应用和设计,且IP核资源丰富,实现起来灵活快速,性能稳定,可以满足高速时序要求。

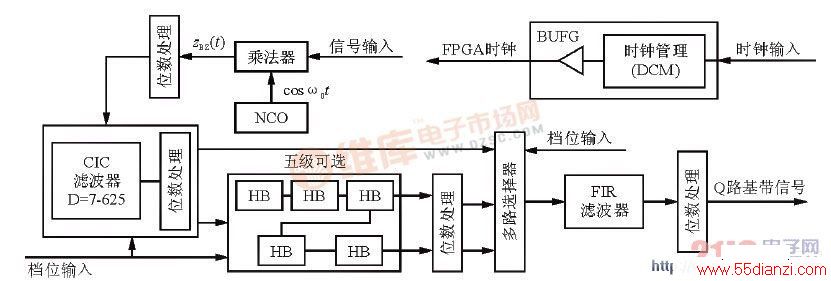

FPGA IP核是预先设计好的功能模块,一般采用参数可配置的结构,并可以通过Core Gener-ator工具调用。数字下变频的设计可用正交数字解调的数控振荡器(NCO) 和乘法器,并分别调用IP核DDS Compiler 4.0和Multiplier 11.2来实现,其中DDS Compiler可以提供SINE和COSINE两个通道。在抽取滤波设计中,图1所示的多组滤波器均可通过调用IP核(CIC Compiler 1.3和FIR Compiler5.0) 来实现。CIC Compiler 1.3可提供输入数据采样率、工作频率、以及可编程抽取等多种参数的设定; HB滤波器和FIR 滤波器均采用FIRCompiler 5.0,该IP核可以导入*.coe格式的滤波系数,并通过导入不同的系数来区分不同类型的滤波器。它同时提供有不同滤波器结构类型的设定,包括乘累加结构、基于DA算法结构和多相滤波结构以及输入数据采样率和工作频率等基本滤波器参数的设定。

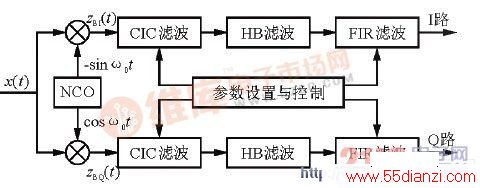

数字下变频模块的整体设计如图2所示,由于I、Q两路对称,为了方便,这里只描述Q路的数字下变频实现过程。本设计采用Xilinx公司的Spartan–3A–DSP系列FPGA芯片来实现,它整合了DSP48A模块,并含有丰富的乘法器资源,适合数字信号处理模块的实现,且成本和功耗都很低。

图2 数字下变频模块整体设计

处理模块按数字下变频原理,可依次实现正交解调、抽取滤波和FIR滤波,最终得到基带信号。该模块共有三个输入,信号输入为A/D转换器的输出序列,位数14-bit,采样率为100MSPS,中心频率为21.4MHz,这决定了数字中频中NCO输出位数可同设为14 -bit,输出频率设为21.4MHz。

时钟输入是A/D转换器输出序列的随路时钟,频率为100MHz,可作为处理模块的工作时钟。

在FPGA设计平台的ISE中,BUFG是全局缓冲,它连接的是芯片中的专用时钟资源,目的是减少信号的传输延时,提高驱动能力,这对于时序电路中的关键时钟信号是非常重要的。DCM是数字时钟管理单元,具有最小的时钟延迟和抖动,故可采用DCM+BUFG方法将时钟输入分配为FPGA时钟。而使用全局时钟资源则可保证时序同步。

带宽输入为分辨率带宽步进输入,它决定了待分析带宽B (RBW) 和滤波器组的抽取。操作时,首先可由待分析带宽确定最后一级FIR滤波器的3dB带宽和输入采样率,然后再根据A/D采样率与FIR输入采样率的比值来确定CIC滤波器抽取因子和HB滤波器级联级数。

另外,在模块整体设计中,位数处理也是一个关键,它由带宽步进输入决定,可调整各个部分的二进制输出位宽。因为滤波的卷积运算为乘累加运算,这会导致滤波器的输出位数增多,可在输出精度和准确度满足要求的情况下,在正交解调和每一级滤波器后做位数处理,这样的方法一是为了防止多余的输出位数在后级滤波器中累加,从而节省FPGA逻辑资源; 二是为了调整滤波器组的输出幅度,以避免在不同带宽选择时输出幅度不一致。