1 前 言

随着数字化电子技术日新月异的发展,借鉴国外先进经验与先进技术推动我国电子设备产业的发展势在必行。复杂可编程逻辑器件(complex programmable logIC device, cpld )作为国外最先进的一代大规模数字器件,以其可靠性高和逻辑设计灵活的优势,在工业控制和军事领域中得到了日益广泛的应用。

机载雷达对发射机控制与保护系统(以下简称控保系统)要求十分严格,不仅要求它具有完备的实时逻辑控制与保护功能,而且对其所处的环境温度与振动条件也要求十分苛刻。基于cpld技术的机载小型化控制与保护,采用了lattice 公司的isplsi1032-60lg可编程逻辑器件,工作温度范围从-55℃到125℃,抗振等性能较好;在设计过程中,应用数字处理技术实现了对雷达发射机的实时与复杂逻辑控制,采用数字时间滤波技术提高发射机控保的i/o抗干扰性能;另外,由于cpld具备良好的现场在线可编程能力,基于cpld的控保系统对中小型发射机来说,在通用化、系列化、组合化应用方面具有较高的推广价值。

2 功能需求

控保系统是发射机系统的重要组成部分。其主要技术要求有:

(1)完成对过温、过压、欠压、真空度下降、管体过流、相关电源等的实时检测。

(2)对发射机进行预热延时处理,预热完成后,按顺序执行开高压、开触发、开激励等过程。

(3)为发射机调制器提供预调脉冲与前级控制脉冲。预调脉冲包括开启脉冲与关断脉冲,预调脉冲需进行逻辑保护,两个脉冲不可同时为高电平。

(4)实现对发射机定时信号的检测,具有过d与过τ保护功能。

(5)控保系统检测到故障时,智能化关闭发射机。

3 硬件组成

雷达发射机控保主要由cpld、运算放大器电路、比较器电路、i/o接口电路、预调脉冲形成电路、控制及显示电路组成。其硬件组成框图如图1所示。

图1中,高压检测电路将传感器检测信号进行放大,并比较产生过压与欠压的ttl接口信号送至cpld,高压信号为模拟量信号,以行波管(travelling wave tube,twt)发射机为例,高压包括twt的阴极高压和收集极高压;过流、过温、钛泵电流检测电路分别提供cpld过流、过温、真空度等相关故障信号;接口电路主要接收雷达信号处理机提供的差分传送开关发射机指令与工作定时信号等;显示电路指示发射机故障信息和工作状态信息。jatg接口提供cpld的在线编程接口。另外,该控保电路还提供了调制脉冲隔离变压器用+20v电源和电路元器件用±12v电源。

4 工作原理

4.1 系统逻辑设计

基于cpld的小型化控保电路核心器件为cpld。系统采用4mHz晶振作时钟基准脉冲,由cpld进行数字计数产生特定的时序关系,根据控制信息、发射机工作状态和故障信息进行综合评估,控保系统将各故障信息进行逻辑处理,产生故障结果,参与各节点的控制,实时保护和控制发射机开关机过程。

发射机控制与保护逻辑关系如图2所示。指令信息包括开关高压指令与开关调制指令,调制器用定时信号有两组,一组为开启脉冲,另一组为关断脉冲,前级激励信号控制导前脉冲形式。

4.2 上电复位与延时

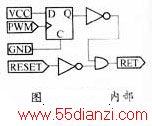

控保上电复位十分重要,这里采用的是硬件外部复位与cpld的逻辑处理复位。其复位电路如图3所示,reset来自于外部rc复位信号,当时钟稳定后,cpld内部产生一个复位信号使得各电路中的d触发器复位,将计数器同步清零。由于电路在上电初始阶段各i/o口电平均处于暂态,没有进入稳定工作状态,这个过程实际上也是等待外围i/o电平建立稳定。

4.3 过d、过τ保护

过d与过τ保护,即,过占空比与过脉冲宽度保护。当出现过d与过τ故障时,立即关断激励与触发,以保护twt等关键性器件。其检测与保护在该系统中是比较难的,脉冲宽度与脉冲重复频率可变这一特点,使得信号时序关系实时处理也比较复杂。而过d与过τ保护原理比较简单。这里举例加以说明。

假设过d保护最大占空比为12.5%,过τ保护最大脉冲宽度为310μs。图4(a)所示给出了待测的脉冲波形,占空比d等于τ/t,图中τ1不等于τ2,t1不等于t2。

用于检测的基准时钟为4mHz,cpld从脉冲上升沿电平翻转开始计数,当电平下降沿翻转后停止计数并锁存数据data1,所计数据为τ的值,它们的分辨率为1/4mhz,误差为±0.25μs。将锁存的数据进行数字比较,当data1大于310/0.25即1240时,发生过τ故障。这里采用able硬件描述语言设计了1240数字比较器,程序如下:

equations

out=(i>=^d1240);

end

脉冲信号上升沿触发d触发器,产生周期脉冲波形如图4(b)所示,当图4(b)中电平为高时对周期t1进行计数,为低时对周期t2进行计数,电平每发生一次翻转,锁存周期数据data2转入下一个周期计数。采用图4(a)脉冲波形上升沿作适当延时后的波形,用于数字比较器比较的触发条件,当8倍的data1大于data2时,即发生过d故障。当过d/τ故障连续出现一定次数后,确认为故障,输出相应故障信号。过d/τ保护逻辑框图如图5所示。图6给出了过d/τ保护实时仿真所得的仿真结果。

4.4 i/o接口的抗干扰处理

真空电子管发射机由于具有高压、大功率的特点,对于低压控保电路而言,具备较高的抗干扰能力十分重要。isplsi1032-60lg型cpld本身的抗干扰能力较好,由于cpld的最大工作频率为60mhz,外部微小干扰信号对于cpld来讲,如不对i/o接口信号作数字滤波处理,cpld将认为这是有效信号参与逻辑判断,实际上,对发射机的控制是不利的,会引发故障虚警,若错误地处理故障虚警信息,关闭发射机,则有可能使得本次试验失败,造成损失,以往应用小规模的集成电路的控保就存在类似的问题,并且很难解决。

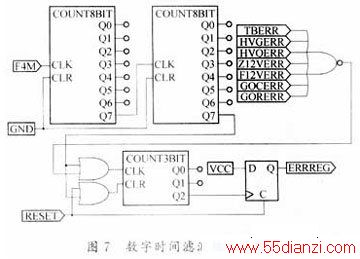

应用cpld技术,解决抗干扰问题应相对容易,图7给出了实际应用中的数字滤波技术原理图,由4mhz信号进行分频计数产生周期为0.25μs ×256×256≈16.4ms的时钟信号,若故障连续出现超过8个脉冲,则认为是真实故障,而干扰信号不会造成故障信号输出。

处理控制信号采用同样的原理,当确认控制信息有效时,进行相关操作。

5 结束语

经试验测试,上述控制与保护硬件电路和软件的设计,具有较好的实时控制能力,在复杂的保护逻辑面前表现出了优越性。基于cpld的控保系统具有性能稳定、抗干扰能力强、体积小、结构紧凑的特点,有较高的推广应用价值。

本文关键字:发射机 EDA/PLD技术,单片机-工控设备 - EDA/PLD技术