3 分辨率带宽设计

本设计的分辨率带宽范围为1kHz~3MHz,按1–3–10步进变换,共8个档位。分辨率带宽步进输入如表1所列,每一个步进均决定了相应的CIC抽取因子和HB的级联级数,同时也决定了最后一级FIR滤波器的输入数据和相应采样率。

表1 抽取因子分配表(采样率100MSPS)

www.55dianzi.com

抽取滤波的目的是将正交解调后的高速率基带信号降低到合适的信号速率,以便常用的基带处理技术使用。在此设定基带信号采样率与分辨率带宽步进为5倍的关系,以计算对应的I、Q基带信号的采样率,进而确定处理模块总的抽取率。由于IP核的抽取率参数只能为整数,所以,要通过对理想抽取率取整,应尽量满足RBW与基带信号采样率的比例关系。而对于低抽取率的档位,只通过CIC抽取就可以完成,但要对HB滤波器进行旁路控制,即HB级联抽取为1。通过滤波器旁路控制和抽取因子可编程实现宽范围抽取因子的调整,进而控制数据流采样,也可以实现分析带宽的变采样率控制。

在图2所示的整体设计框图中,CIC滤波器是抽取部分的第一级,可实现高速抽取,但其通带、阻带特性的可控性不强。通过IP核可设置抽取率(R) 和级数(N) 等参数,而且操作简单。

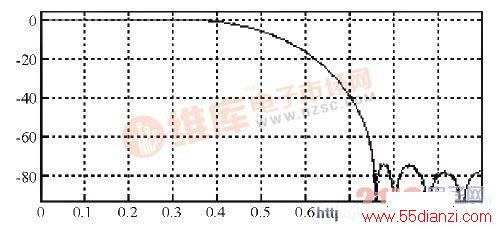

HB滤波器是抽取部分的第二级,单级抽取因子固定为2,有3级级联和5级级联两种情况,各级均采用归一化频率设计方法,以避免重复设计。通常采用MATLAB的FDATOOL工具来设计滤波器,并以RBW滤波器输入信号采样率的2倍作为归一化参考频率,同时保证FIR滤波器通带频率范围内的信号无衰减。由于FIR滤波器的通带设定为0.2,且HB滤波器在此主要做为抽取滤波器,故设通带频率上限为0.21,滤波器阶数为19阶,图3所示是半带滤波器(HB) 的频率响应曲线。半带滤波系数为对称系数且有将近一半的系数为零,19个滤波系数只有6个参与乘法计算,故不会消耗大量的乘法器资源,另外,抽取部分I、Q两路的数据流速率较高,故采用乘累加结构搭建HB滤波器,以满足高速的时序处理要求。

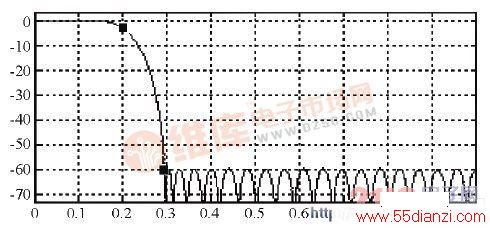

在设计各个分辨率带宽步进输入所对应的RBW滤波器时,为了节约FPGA逻辑资源和简化设计,也可以采用归一化频率设计方法,这样可以使I、Q支路各设计一个RBW滤波器。由于FIR滤波器的输入采样率fs越大,滤波器的最小阶数越高,因而选择3dB带宽与采样率按0.2的归一化比例来设计滤波器的频率响应,且FIR滤波器不进行抽取,其输入采样率等于I、Q基带信号采样率。根据I、Q路信号的归一化带宽0.20可设定RBW滤波器的通带频率上限为0.20,阻带频率下限为0.29,滤波器阶数为47 阶,阻带衰减为60dB,波形因子SF60/3 =B60dB/B3dB =0.29/0.20≈1.45,图4所示FIR滤波器的频率响应曲线。

将生成的*.coe格式的滤波系数可以导入FPGA中所调用的IP核中,考虑到FPGA乘法器资源有限,由于输入数据经前面抽取,其数据率已降低,这里采用基于DA算法结构来搭建RBW滤波器。

图3 半带滤波器(HB) 频率响应

图3 半带滤波器(HB) 频率响应

图4 分辨率滤波器(FIR) 频率响应

4 结束语

采用FPGA硬件并调用各类IP核来实现全数字中频技术的应用方法,其时序性能稳定,可以很好的满足高速、实时的信号处理要求。在频谱仪分辨率带宽设计中,结合范围为1kHz~3MHz的可程控分析带宽,可以采用多速率信号处理技术来降低数字信号的采样率,并为数字幅度/相位检波、视频检波、DSP开发以及实现FFT等后续信号的频谱分析进行准备。该数字中频处理模块也能应用于网络分析、通信分析、雷达信号分析等其他设计,而且可以有效减小系统体积,保证设计的可靠性。