内容摘要: 介绍一种数字中频恢复系统,该系统分为光纤接收单元、FPGA核心单元和QDUC单元。光纤接收单元采用高速串行器/解串器TLK1501,完成高速串行数据的串行转换。FPGA核心单元对数据进行解码、检验、配置TLK1501和AD9957。QDUC单元实现基带信号的上变频和D/A转换。测试结果证明,系统具有实时性好、工作稳定、抗干扰性强的优点。

关键词 光纤传输;FPGA;数字上变频器

直接数字频率合成(Direct Digital Synthesizer,DDS)作为一种先进的信号产生技术,与传统的频率合成技术相比,DDS具有分辨率高、转换速度快、功耗低和成本低等优点,经过40年的发展,已被广泛用于数字信号处理、软件无线电等领域。在现在的雷达系统中,高速高宽带是现行的趋势,传统的并行传输技术由于存在码间串扰、串音干扰和直流偏移等缺点,难以满足高速高带宽的传输要求。目前国内外有关雷达高速宽带信号接收和恢复技术的研究很广泛,多采用软硬件相结合的设计方式,系统灵活,同时满足信号实时输出的要求。

文中讨论的基于AD9957的多波形雷达信号恢复实现方案,融合了光纤通信、现场可编程门阵列(FiELD-Programmable Gate Array,FPGA)和DDS等技术,具有误码率低、抗干扰性强、实时性强、数字化、可编程和多功能等特点。

1 系统设计方案

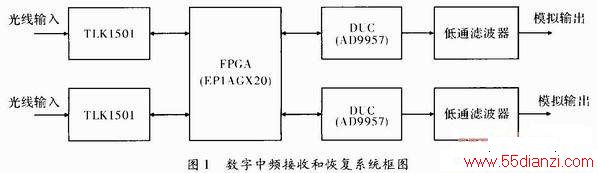

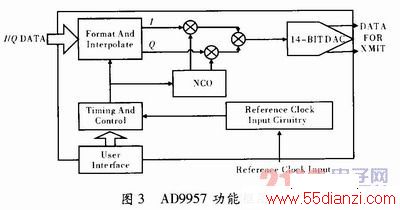

系统的设计结构如图1所示。主要有光纤接收电路、FPGA单元、正交数字上变频器(Quadrature Digital Up Conversion,QDUC)及信号调理电路组成。光纤传输的是已经被编码、校验、成帧后的数据,其接收电路主要由TLK1501电路完成,负责将光电转换后的串行数据流转换为并行数据。FPGA采用ALTEra公司带有收发器的EP1AGX20CF48416N,完成光纤数据的解帧、校验和解码,剥离出有效的数据。同时,光收发器也可直接与FPGA连接,增强了系统的灵活性。正交数字上变频器(QDUC)采用AD9957实现,完成基带信号的数字上变频(Digital Up Convei ter,DUC)和数模转换(Digital Analog Converter,DAC)。信号调理电路将模拟信号滤波提纯。

2 TLK1501接口设计

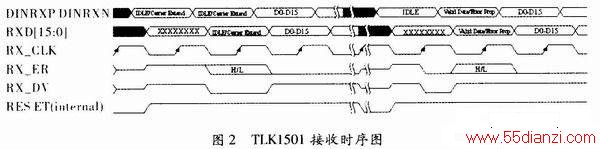

TLK1501是德州仪器推出的0.6~1.5 Gbit·s-1高速串行器/解串器,内部集成了8b/10b编解码模块。TLK1501有两种工作模式,一是收发模式,二是只发模式。在收发模式下,TLK1501的发送和接收需要严格的同步,如果接收侧断开,则发送端自动发送同步码,直到接收侧重新同步。在只发模式下,TLK1501只是单向发送,接收端输出为高阻态。在实际使用中,本系统用到了TLK1501的第一种工作模式,但只用到了TLK1501的接收数据功能。在接收数据时,TLK1501的DINRXP/DINRXN管脚上的高速串行数据流经过串并转换和10b/8b解码后恢复成16 bit并行数据,当RX_DV为高同时RX_ER为低时,在RX_CLK上升沿时,RXD[15..0]端口输出有效数据。应用中TLK1501的接收时序如图2所示。

3.1 串行接口设计

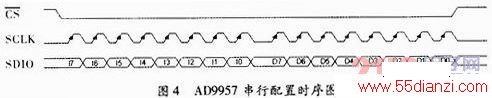

AD9957的配置是通过同步串行通讯端口实现的,可以方便地与多种工业用微处理器接口连接,并兼容多种同步传输格式。本设计通过在FPGA内部编写同步串行通讯逻辑实现对AD9957的配置。其串行通讯周期分为两个阶段,第一阶段是传输指令阶段,将指令字写入AD9957,指令字主要包括要访问的寄存器地址,以及将进行的数据传输是读操作还是写操作。第二阶段是数据传输阶段,将数据从串行端口控制器向串行端口缓冲区传输数据,传输的Byte数取决与要访问的寄存器。其时序控制图如图4所示。

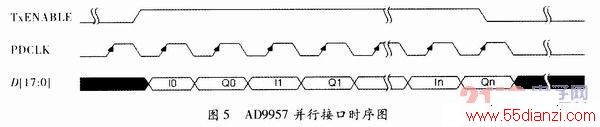

3.2 并行接口设计

AD9957有一个18位的并行数据输入端口,在QDUC模式下,FPGA将I/Q数据基带数据交替的输入到AD9957内部。基带数据的时钟PDCLK由AD9957提供,最高支持250 MHz的并行数据时钟,同时也是并行数据的采样时钟。系统中PDCLK工作在200 MHz。AD9957在TxENABLE的上升沿准备接收第一个I字,在PDCLK的有效沿上,第一个I字被锁存至器件,PDCLK的下一有效沿锁存一个Q字,依次类推。需要特别注意的是:确保向器件中送入偶数个数据,因为器件必须捕捉到一个I字和一个Q字,然后才能使接收到的数据沿着信号链处理。

值得注意的是,AD9957的并行数据传输速度较高,容易发生调制数据时序问题,会导致I/Q基带数据相位不平衡等问题,严重时,会导致调制数据错误。因此,在进行硬件设计时,需严格按照AD9957的并行数据传输时序要求操作,必要时在FPGA内部对时序进行优化,以提高数字正交调制器的调制效果。

www.55dianzi.com

4 系统工作原理

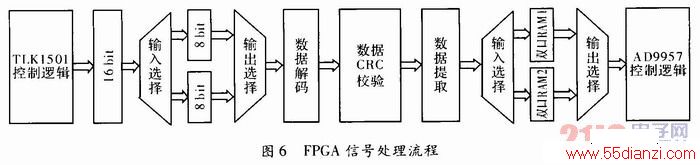

FPGA是系统的核心,FPGA从TLK1501中接收数据,经过处理后,将有效数据送到AD9957并行数据输入端口,由AD9957完成信号的恢复。

系统中光纤的传输速率为1.2Gbit·s-1,在TLK1501中经过10b/8b解码后,其有效数据的传输速率为960 Mbit·s-1,经过时钟恢复,数据对齐后,转换为16位并行数据输出,等效并行传输速率为60 MHz,因此,FPGA需要为TLK1501提供60 MHz的配置时钟。

TLK1501中接收到了并行数据,在FPGA中需进一步的处理,分离出帧命令字,提取有效数据,并进行CRC校验,其信号处理流程如图6所示。

编解码过程是面向字节,既需要将TLK1501接收到的每个16bit数据拆解成2Byte,再依次对每一个Byte进行处理。因此,系统设计了一个乒乓操作,其操作过程下文将详细叙述。在数据编码时,采用了比特填充法,即将数据中出现的每个0X7E转变成0X7D和0X5E,每个0X7D转变成0X7D和0X5D。解码过程是编码的逆过程,即将数据中两个连续出现的0X7D和0X5D还原成0X7E,将两个连续出现的0X7D和0X5D还原成0X7D。

循环冗余检验码,是一种检出概率高、易于硬件实现的检错码。系统采用的CRC生成多项式为G(x)=![]() ,系统借助FPGA寄存器资源和并行处理数据时高速流水线优势,根据数学算法上的超前位计算原理,系统实现高速有效的CRC计算,很好地使资源和速度平衡。在CRC校验正确的情况下,进行下一步处理。当前帧输出的前25 Byte为系统的控制字,最后的2 Byte为CRC校验的高8位和低8位,在此单独分离出来,剩余的数据位为有效数据。

,系统借助FPGA寄存器资源和并行处理数据时高速流水线优势,根据数学算法上的超前位计算原理,系统实现高速有效的CRC计算,很好地使资源和速度平衡。在CRC校验正确的情况下,进行下一步处理。当前帧输出的前25 Byte为系统的控制字,最后的2 Byte为CRC校验的高8位和低8位,在此单独分离出来,剩余的数据位为有效数据。

在进行数据缓存时,系统采用乒乓操作实现。提取出来的有效数据通过“输入选择”单元将数据流交替分配到两个数据缓冲区,在本系统中,数据缓冲模块采用双口RAM实现。在第一个缓冲周期,将输入的数据暂存到“双口RAM1”,在第2个缓冲周期,通过“输入选择”单元的切换,将输入的数据暂存到“双口RAM2”,同时“双口RAM1”中暂存的第1个周期数据通过“输出选择”单元的选择,由AD9957控制逻辑按照时序要求并行输出;在第3个缓冲周期通过“输入选择”单元的再次切换,将输入的数据暂存到“双口RAM1”,同时“双口RAM2”暂存的第2个周期数据通过“输出选择”单元的切换,由AD9957控制逻辑时序要求并行输出,如此循环。通过“输入选择”单元和“输出选择”单元按时钟节拍、相互配合的切换,将经过缓冲的数据流连续地送到“数据流运算处理模块”进行运算或处理,实现了对数据流进行流水线式的处理,完成数据的无缝缓冲与处理。

本文关键字:暂无联系方式综合-其它,单片机-工控设备 - 综合-其它