随着软件无线电在中频领域的广泛应用,采用数字信号处理技术设计了基于FPGA全数字中频跟踪接收机并应用于遥感卫星天线接收系统中。给出了详细的理论说明和体统组成。该接收机结构简单,成本低,调试方便。在测试和实际应用中,该跟踪接收机输入信号的动态范围大,AGC和误差电压精度等指标较模拟接收机都有显著的提高。

随着软件无线电技术和全数字接收机技术的迅速发展,以及现场可编程门阵列FPGA规模的不断壮大,用FPGA实现中频数字跟踪接收机已经成为必然的趋势。本文设计的中频跟踪接收机中包括了A/D变换,数字正交混频以及数字滤波等模块。主要的功能模块分为中频接收模块和误差信号提取模块。

经过测试,系统能够完成单脉冲跟踪体质天线的自动跟踪任务,实现了对中频调幅信号的采样,下变频,解调等功能。系统结构简单,体积小,成本低,有良好的通用性。

1 总体设计

自动跟踪接收系统是遥感卫星地球站的一个组成部分,它接收来自天线的卫星数据信号(和信号)和角度误差信号(差信号)经变频,滤波,放大,检波,解调后向伺服系统提供所需要的角度误差信号,控制天线的方位轴,俯仰轴和方位轴向角度误差小的方向转动,实现对目标的跟踪。

其中中频接收本分完成差信号的幅度检波输出视频信号和信号强度的提取,误差信号提取模块完成角度误差信号的解调,斜率补偿、相位补偿和时分信号的输出。

2 数字中频接收机设计

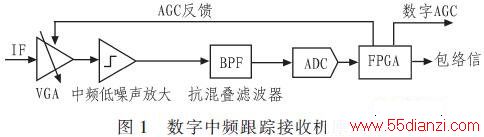

数字中频接收机包括中频采样、A/D变换、数字AGC、数字下变频、AM检波等。原理框图如图1所示。

中频信号经过一个大动态压控放大器、中频低噪声限幅放大器和一个抗混叠带通滤波器进入A/D采样,采样后的数据进入FPGA计算,输出AGC信号和基带信号进入下一级。数据在FPGA中完成数字下变,CIC抽取滤波,FIR低通滤波,AM检波,数字AGC等计算。

2.1 中频采样和A/D变换

本文提到的中频数字跟踪接收机是70 MHz中频信号输入,信号带宽为12 MHz。输入信号经抗混叠滤波器后,进行A/D采样。采用欠采样的方法来求的适合的采样率。根据通带采样定理,采样率必须满足一下条件:

![]()

其中,fs是采样频率,fh、fl分别是信号的上、下限频率,BW=fh-fl是信号带宽,m为正整数,可去的值分别为:2~6。

可见,最低采样率可以取到25.3~25.6之间,但是采样率太低会给滤波器的设计带来难度。最后根据Heisenberg不定性原理来估计采样率与分辨率的关系,以及采样率与分辨率对信噪比,ADC动态范围的影响,计算最佳采样率(正交采样)选择采样频率fsopt=56 MHz,分辨率为16位。

2.2 数字下变频的实现

用56 MHz的采样频率对70 MHz的信号进行采样,带通采样相当于将信号以56 MHz的间隔进行频谱搬移,所以采样后的信号,只需要下变频14 MHz就可以得到基带信号。采样后的调幅信号与数字本振频率为14 MHz的正余弦信号进行数字混频,产生同相和正交两路基带信号。同相分量中含有基带分量和二次谐波分量,只要通过低通滤波器就可以得到基带分量。正交分量中只包含二次谐波分量,通过低通滤波器可已完全滤除。为了节约系统资源,所以设计NCO只需要产生同相分量。选择固定系数法来产生正弦信号和余弦信号,避免由于相位截短带来的误差。正交本振详细取值如下:

cos(0)=1;cos(0.5π)=0;cos(π)=-1;cos(1.5π)=0;

sin(0)=0;sin(0.5π)=1;sin(π)=0;sin(1.5π)=-1。

本振信号的幅度值只有{0,1,-1},用Verilog编程实现直接与ADC输出相乘实现混频,这种方法实现数字本振信号精度非常高。

数字下变频部分设计的运算都集中在数字滤波部分,为减少运算首先对I、Q信号进行CIC抽取。CIC滤波器是一种基于零极点相抵消的FIR滤波器。本文设计是一个5级级联32倍抽取CIC滤波器,包括5级积分器,10倍抽取器和5级梳状滤波器。它们分别用累加器、序列变换和减法器用Verilog编程实现。

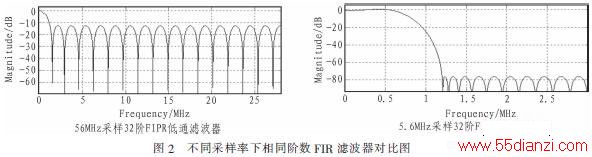

最后通过一个32阶的FIR低通滤波器:通带截止频率为0.6 MHz,阻带起始频率为1.2 MHz。用MATLAB的Smuilink的数字信号处理工具计算滤波器系数。比较抽取前后的滤波器以及资源占用情况。很明显抽取后的FIR低通滤波器要优于抽取前的,如果要在高采样率下达到抽取后的效果,就需要滤波器有个高的阶数,从而占用更多的资源。

2.3 包络检波

包络检波由开平方![]() 根和环路滤波器组成。经过抽取的信号经过开平方根后得到信号能量,再送到环路滤波器除去高频分量,得到信号包络信息。环路滤波是由一个2阶IIR低通滤波器和一个1阶IIR低通滤波器级联组成,构成一个三阶窄带滤波器,可以得到信号长期电平估计。这样可以保证增益因子不会因为接收信号的快速波动而发生较大变化。

根和环路滤波器组成。经过抽取的信号经过开平方根后得到信号能量,再送到环路滤波器除去高频分量,得到信号包络信息。环路滤波是由一个2阶IIR低通滤波器和一个1阶IIR低通滤波器级联组成,构成一个三阶窄带滤波器,可以得到信号长期电平估计。这样可以保证增益因子不会因为接收信号的快速波动而发生较大变化。

2.4 数字AGC设计

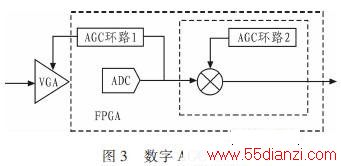

为保证中频接收机中ADC的动态范围和精度,要求AGC的动态范围大,即从可变增益放大器的输出中提取幅度并反馈控制其增益,使输出信号电平基本保持恒定且不溢出。可控增益范围和时间常数是AGC的两个重要指标。由于低轨卫星的发展和天线的单脉冲跟踪体质要求跟踪接收机的动态范围要在70 dB以上,模拟AGC很难达到如此高的要求。本文中要求跟踪接收机采用两级AGC,动态范围在100 dB以上,时间常数在100 ms一下可调。设计如图3所示。

图3是一种数字AGC的方框图,它采用了模拟和数字增益两级AGC控制。接收到的中频信号经电压控制的可控放大器放大进入A/D采样,采样后输入数字信号处理器,经过AGC1系统产生中频放大器控制电压,AGC1的作用是使输入信号的峰一峰值限制在ADC的最大允许电压之内,防止输入采样的ADC溢出。数字放大器的增益由软件AGC2控制,使输出的信号电平恒定。

设AGC1的阈值电压设为E,信号输入值设为x(n)·k(n)|>E时,放大倍数Gg偏大,需减小放大倍数,当|x(n)|<E时,放大倍数Gn偏小,需增大放大倍数。如果|x(n)|>E时,则Gn增益在上升时间内应该下降,即降低增益应:△G=20(log|x(n)|-logE)dB因此每一个样点增益应下降20(log|x(n)|-logE)/N,其中N与AGC的时间常数有关,N=上升时间(或释放时间)×抽样频率。假设AGC1的总增益控制量为a,单位为dB,电压变化范围为b则有![]() 单位为V,则AGC1电压在每一个样点应增加,将(2)式整理,令变量

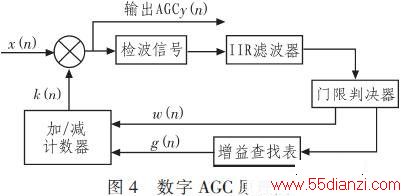

单位为V,则AGC1电压在每一个样点应增加,将(2)式整理,令变量![]() ,这是与AGC的时间常数。AGC2的算法与AGC1相似。下图给出了AGC2的算法实现框图如图4所示。

,这是与AGC的时间常数。AGC2的算法与AGC1相似。下图给出了AGC2的算法实现框图如图4所示。

门限判决模块的作用是限制加减计数器控制信号的波动,防止环路振荡。其内部设有2个门限,2个门限之间的范围即为AGC输出信号的波动范围。为了防止AGC发生振荡,该范围应该在满足解调要求的动态范围条件下足够宽,而不是1个恒定不变的电平值。该模块首先对来自包络检波模块的信号进行截位处理,以便与16位门限进行比较,判决过程与外部AGC相似。根据指标要求,数字AGC控制范围为30 dB,系统调整步进量为0.1 dB,所以查找表地址设计为64位即可满足要求。环路增益步进量控制信号是滤波器输出信号电平的非线性函数。假设估计的输入信号电平过低或过高,计数器的步进量按标度给出,以降低AGC的增益调整时间,在这个时间内使信号调整到门限判决模块的两门限之间。步进量设置为非线性,是为了防止当信号接近最佳工作点时发生环路振荡。当信号电平接近最佳电平范围时,增益调整的步进量减小,以确保整个环路的稳定性。

本文关键字:接收机 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术