5.驱动字符型液晶显示器实验

1、实验要求驱动1602字符型液晶显示一行内容。

2、实现方法液晶的读写速度比较慢,为了与高速的CPLD( FPGA)相匹配,就要降低读写速度。为此,我们建立一个16位的计数器对MCU&CPLD DEMO试验板上的24MHz频率进行分频,使得每两次写入的时间间隔大于1毫秒,这样较好地满足了液晶的读写速度要求。

3、程序设计在D盘中先建立一个文件名为CPLD1602的文件夹,然后建立一个CPLD1602的新项目,输入以下的源代码并保存为CPLD1602.v。

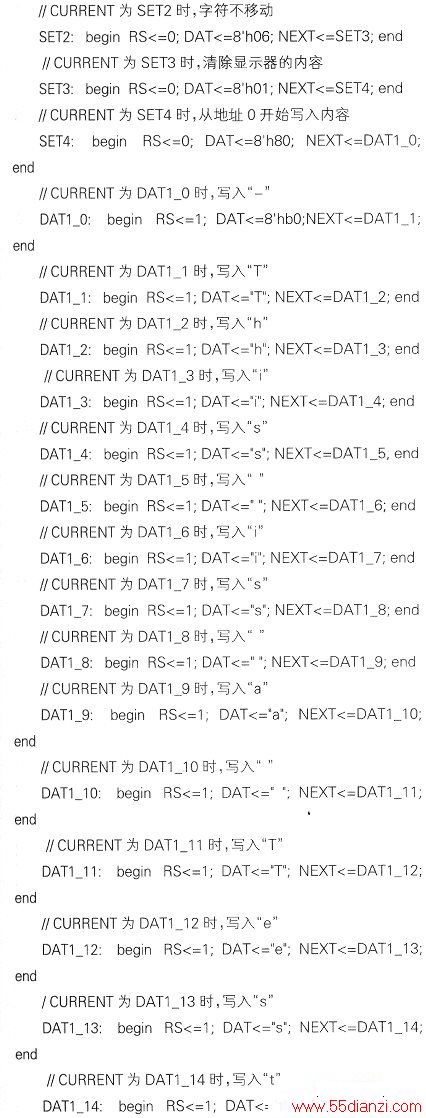

module CPLD1602(CLK,RS,RW,EN,DAT);∥模块声明及输

入输出端口列表

input CLK; ∥定义输入端口

output [7:0] DAT; ∥定义输出端口

output RS,RW,EN; ∥定义输出端口

reg E: ∥定义E为寄存器类型的

1位变量

reg [7:0] DAT; ∥定义DAT为寄存器类型

的8位变量

reg RS; ∥定义RS为寄存器类型

的1位变量

reg[15:0] COUNTER; ∥定义COUNTER为寄存

器类型的16位变量

∥定义CURRENT、NEXT为寄存器类型的6位变量

reg[5:0] CURRENT,NEXT;

reg CLKR; ∥定义CLKR为寄存器类

型的1位变量

reg[1:0] CNT; ∥定义CNT为寄存器类型

的2位变量

parameter SET0=6'd0; ∥常量定义

parameter SET1=6'd1; ∥常量定义

parameter SET2=6'd2; ∥常量定义

parameter SET3=6'd3; ∥常量定义

parameter SET4=6'd4; ∥常量定义

parameter DAT1_0=6'd5; ∥常量定义

parameter DAT1_1=6'd6; ∥常量定义

parameter DAT1_2=6'd7; ∥常量定义

parameter DAT1_3=6'd8; ∥常量定义

parameter DAT1_4=6'd9; ∥常量定义

parameter DAT1_5=6'd10; ∥常量定义

parameter DAT1_6=6'd11; ∥常量定义

parameter DAT1_7=6'd12; ∥常量定义

parameter DAT1_8=6'd13; ∥常量定义

parameter DAT1_9=6'd14; ∥常量定义

parameter DAT1_10=6'd15; ∥常量定义

parameter DAT1_11=61d16; ∥常量定义

parameter DAT1_12=6'd17; ∥常量定义

parameter DAT1_13=6'd18; ∥常量定义

parameter DAT1_14=6'd19; ∥常量定义

parameter DAT1_15=6'd20; ∥常量定义

parameter NUL=6'd21; ∥常量定义

∥一一一一一一一.

∥每当CLK产生上升沿时,执行一遍begin_end块内的语句

always @(posedge CLK)

begin//begin_end块开始

COUNTER=COUNTER+1; 11计数器COUNTER加1

if(COUNTER==15'h0001) 11每当计数值等于1时(两次之

间的间隔为1.36毫秒)

CLKR=~CLKR; ∥CLKR翻转

end ∥ begin_end 块结束

∥一一一一一一一一

∥每当CLKR产生上升沿时,执行一遍begin_end块内的语

句

always @(posedge CLKR)

begin//begin_end块开始

CURRENT=NEXT; ∥将下一变量NEXT赋予当前

变量CURRENT

case(CURRENT)∥case语句,根据CURRENT的

值,产生散转分支

∥CURRENT为SETO时,选择液晶为8位数据传输,单行显

示

SETO: begin RS<=O; DAT<=8'h34; NEXT<=SET1; end

∥CURRENT为SET1时,显示屏开启

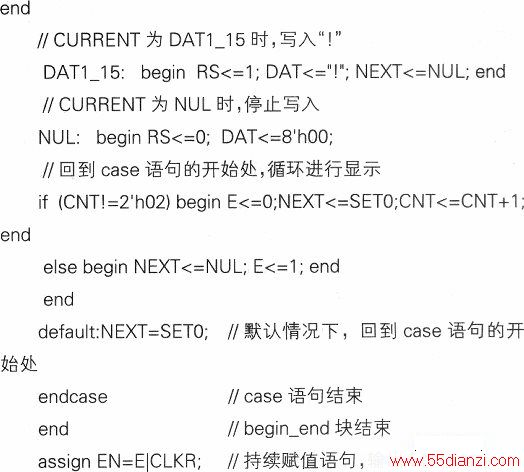

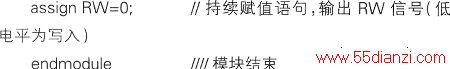

SETl: begin RS<=O; DAT<=8'hOc; NEXT<=SET2; end

驱动字符型液晶显示器实验的引脚分配

源代码输入完成后,我们将器件选择为EPM7128SLC84-15。引脚分配需要参考MCU&CPLDDEMO试验板的电路原理,这里的引脚分配见表7。器件编译通过后,可根据需要进行仿真,接下来进行*.pof至*.jed的文件转换,最后将*.jed文件下载到ATF1508AS芯片中。

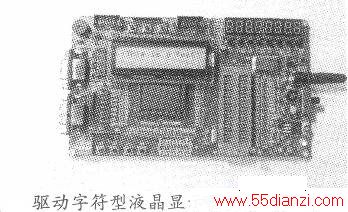

在MCU&CPLDDEMO试验板上,将一个1602字符型液晶模组正确地插入LCD16*2单排座,上电以后,我们看到屏幕的第一行显示“-ThisISATest!”,图3为实验的照片。

6.串口接收实验

1、实验要求在PC机上使用串口调试软件发送一个字节,MCU&CPLDDEMO试验板收到后驱动发光二极管进行相应的指示。

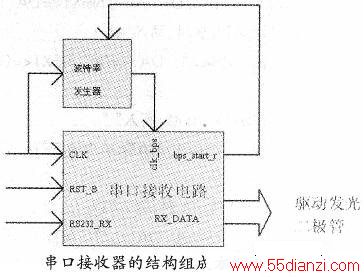

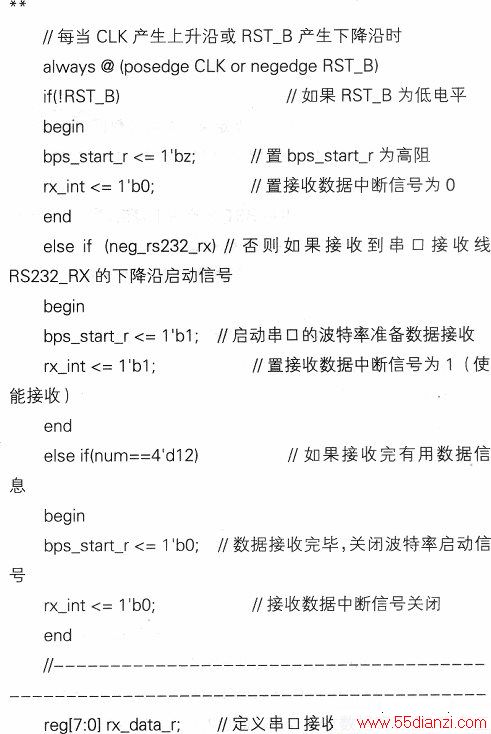

2、实现方法串口接收器的结构组成方框图见上图。我们以波特率9600、数据位8位、停止位1位为例进行设计。因为MCU&CPLDDEMO试验板上的有源晶振频率为24MHz,所以波特率9600的分频数是24000000÷9600=2500,波特率9600的分频数一半是24000000÷9600÷2=1250。

平时,RS232_R×为高电平。当串口接收电路检测到输入端RS232_R×出现下降沿时,将bps_start_r置高,启动波特率发生器,产生波特率时钟脉冲clk_bps_r,同时开始从RS_232RX端接收串行数据,并且同步启动移位次数计数器工作,每个波特率时钟的高电平接收一位数据。在标准的接收模式下,只有1+8+1(2或3)=12位的有效数据。收到停止位后,移位次数计数器清零,并将数据锁存到输出寄存器中,驱动发光管指示。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:CPLD、FPGA设计