PLC主机是通过背板总线支持扩展模块的连接, 背板总线是PLC 主机同I/O扩展模块之间的高速数据通路,支持主机和扩展模块之间的I/O 数据刷新。背板总线的技术水平决定了PLC 产品的I/O 扩展能力,是PLC 设计制造的核心技术。目前,PLC 大多采用串行通信技术实现背板总线,串行总线引线少、硬件成本低,跟并行总线相比不容易受干扰,串行总线可以提高在恶劣的工厂和工业环境下自动化设备的可靠性。用于串行通信技术的可选类型包括I2C、UART、SPI、USB 和以太网等,一般来说,很多作为PLC 主芯片的单片机自身都集成了这些外设部件。但是单片机内部集成的I2C、UART、SPI 外设通信速率太慢,根本不能满足底板总线的通信速度要求。USB 和以太网的通信速度虽然很快但由于它们都是通用的接口,在通信协议处理时需要单片机的干预, 单片机处理数据速度较慢,因此整体通信速度仍然很慢。一台大型的PLC 采集上千点I/O 数据的时间一般不到1ms,要满足如此高速的通信要求必须设计专门的背板总线。

1 背板总线工作原理

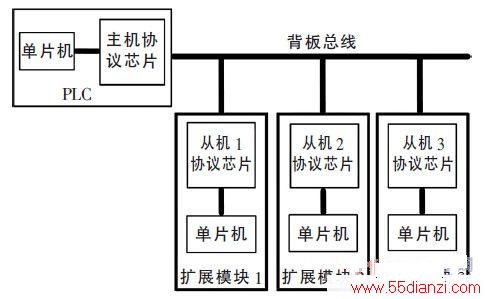

如图1 所示,基于背板总线的数据通信流程如下:

(1)PLC 主机的命令通过主机协议芯片发送到背板总线;(2)从机协议芯片把接收到的命令给扩展模块的单片机, 某一个扩展模块的单片机做出应答,通过从机协议芯片把应答数据送往背板总线;(3)主机协议芯片收到应答数据,并送往PLC主机的单片机。

图1 背板总线通信框图

PLC 主机发往背板总线的数据可以分成两类:一类是I/O 刷新数据,具有周期性,数据交换非常频繁;另一类是诊断性数据,具有非周期性,出现机会较少。

2 协议芯片设计

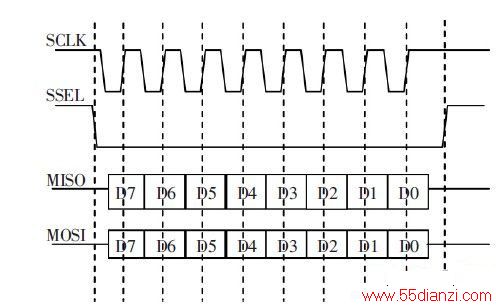

本设计定义背板总线采用类似SPI 串行通信的规格,用于通信的引线共4 根,包括时钟信号SCLK、片选信号SSEL、写数据引线MISO 和读数据引线MOSI;支持主机和从机同时收发数据,数据位格式如图2 所示,数据帧在SSEL 信号为低电平时传输。

图2 背板总线数据规格

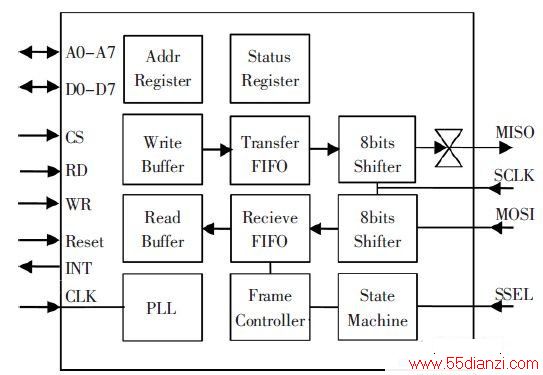

主机和从机协议芯片的内部结构框图相同,如图3 所示。

协议芯片内部有状态机控制器、帧控制器、移位寄存器、接收/发送FIFO 和读写缓存。单片机发送的周期性、非周期性数据帧,首先都写到写缓存,在发送FIFO 中进行排队发送,在SPI 时钟SCLK 的驱动下数据帧被转换为串行数据发送到背板总线;在SPI 时钟的作用下, 接收来自背板总线上的串行数据;在状态机和帧控制器的协调下,接收FIFO 中的有效数据帧被提取并放进读缓存区,等待单片机来读取,如果是非周期性数据则发中断信号通知单片机来取数据。读缓存中的周期性数据是可以覆盖的,新接收到的周期性数据直接覆盖旧的周期性数据,而非周期性数据是单独存放的,不能覆盖,由单片机读取并清除。

图3 协议芯片内部结构框图

协议芯片使得外接的单片机可以在空闲的情况下访问读缓存和写缓存,单片机不必频繁地通过中断技术处理周期性数据,也使得PLC 主机可以无等待地访问从机的周期性数据。

3 基于CPLD 的协议芯片实现3.1 CPLD 芯片选型。

本设计选用lattICe 公司的MachXO 系列芯片,该系列CPLD 集成了部分FPGA 的功能, 除了内置丰富的LUT 资源以外,还有大量分布式的SRAM 位和嵌入式的专用于FIFO 设计的SRAM 块, 并有模拟锁相环(PLL)支持时钟信号的倍频、分频等,I/O引脚可配置成1.2/1.5/1.8/3.3V 电平兼容。

3.2 基于Verilog HDL 语言的硬件程序设计

本设计采用Verilog HDL 语言进行协议芯片的程序设计,Verilog HDL 语言是一种硬件描述语言,设计数字芯片时可以按照层次描述,并可以进行时序建模。本设计采用混合设计模式,主要设计的模块有状态机、协议帧检测、FIFO 控制器设计等。

1)状态机设计。

协议芯片的顶层模块是状态控制器部分,协议芯片共有四个状态, 分别处理基于Verilog HDL 程序语言的状态机描述伪代码如下:

2)协议帧检测。

本协议芯片的帧校验和采用简单的加和形式进行,在接收一方,如果数据帧中有用数据的加和同后续的校验和字节相同,则协议是正确的,否则丢弃该帧。协议帧校验和计算的代码如下:

3)FIFO 设计。

FIFO 利用了MachXO 系列CPLD 的嵌入式SRAM 块的资源,Lattice 公司的ispLEVER 7.0 软件提供了可配置的IP 软核,该软核可以采用基于嵌入式SRAM 块实现, 也可以使用查找表实现,FIFO 的IP 核框图如图4 所示,FIFO 的可配置参数包括FIFO字节深度、EmptyFull、Almostempty 和AlmostFull触发字节深度、数据宽度、大小端模式等。

图4 可配置FIFO 控制器IP 软核框图

用Verilog HDL 语言实现的发送和接收FIFO控制器的实例代码如下:

3.3 协议芯片综合

Verilog HDL 程序通过Lattice 公司的CPLD 开发软件ispLEVER 7.0 进行编译、综合,多次尝试后最终选择了Lattice 公司MachXO 系列CPLD 中的MachXO2280 芯片, 综合后的主机协议芯片占用CPLD 资源的60%左右, 从机协议芯片占用CPLD资源的45%左右,FIFO 控制器充分利用了MachXO2280芯片内部的嵌入式RAM 块, 同时利用了锁相环实现高频率的时钟工作。最后通过LSC ispVM(R)System 烧写软件经JTAG 口下载到CPLD 芯片中进行协议芯片功能验证测试。

4 结语

本文设计的背板总线协议芯片在背板串行总线时钟频率为25MHz、信号电平为LVTTL,底板引线长度为40cm,1 台主机连接3 台扩展模块的情况下工作稳定并通过了群脉冲试验,验证了这一组协议芯片的设计是成功的。由于该组协议芯片是针对PLC 的周期性和非周期性数据传送专门设计的,硬件实现的协议帧控制器支持高速率通信、支持数据帧检验功能,避免了数据传送的错误,大大降低了外围单片机的软件开销,增强了可靠性,是一组非常适合用于PLC 背板总线或者需要多模块协同工作的背板总线系统协议芯片。

本文关键字:接口 PLC工业控制,电器控制 - PLC工业控制