引言

传统测试系统由于专用性强、相互不兼容、扩展性差、缺乏通用化、模块化,不能共享 软硬件组成,不仅使开发效率低下,而且使得开发一套复杂测试系统的价格高昂[1]。 目前,传统的分析仪表正在更新换代,向数字化,智能化方向迈进[2]。改变以往由仪器 生产厂家定义仪器功能、用户只能使用的局面,使用户可自定义仪器、根据不同测试需求对 仪器进行重构,已经成为现代测试技术发展的一个重要方面。由于其能够大大减少测试设备 的维修成本、提高资源利用率,可重构仪器技术已引起高度重视。

1 可重构技术

目前对可重构性还没有形成公认的定义。可重构性一般是指在一个系统中,其硬件模块 或(和)软件模块均能根据变化的数据流或控制流对结构和算法进行重新配置(或重新设置)。

在可重构系统(Reconfigurable System)中,硬件信息(可编程器件的配置信息)也可 以像软件程序一样被动态调用或修改。这样既保留了硬件计算的性能,又兼具软件的灵活性。 尤其是大规模可编程器件FPGA 的出现,实时电路重构思想逐渐引起了学术界的关注[3]。可 重构的实现技术又很多种方式,包括DSP 重构技术、FPGA 重构、DSP+FPGA 重构、可重 组算法逻辑体系结构、可进化硬件(EHW)、本地重构/Internet 远程重构、SOPC/SOC 重构。

可重构技术具有以下优点:

1)可重构技术能够高效地实现特定功能。可重构逻辑器件上都是硬连线逻辑,它通过 改变器件的配置来改变功能。2)可重构技术能够动态改变器件配置,灵活满足多种功能的 需求。3)可重构技术适合恶劣工作环境下的应用。利用可重构逻辑器件的一个优势是不需 要微处理器必需的散热系统,大大减少了电子产品占据的空间。4)可重构技术具有强大的 技术支持来加速产品开发。5)可重构技术的使用能够大大降低系统成本。另外,对于不会 同时被使用的功能,可考虑利用动态重构技术在不同的需求时段里分别实现,做到“一片多 用”,节省了资源、空间和成本。

2 可重构智能仪器硬件设计

2.1 可重构仪器硬件结构

可重构智能仪器技术将先进的微电子技术、半导体技术和微处理器技术引入仪器设计领 域,通过构建通用的硬件平台,最终由用户通过选择不同的软件来实现不同的仪器功能,因 此软硬件在可重构仪器设计技术中同样关键。

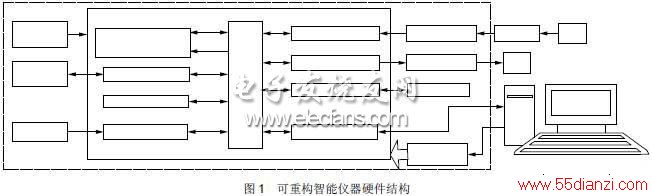

可重构智能仪器硬件结构由 Nois II 处理器系统(包括可重构FPGA 芯片、FPGA 片外 系统)和计算机组成,其硬件结构框图如图1 所示。

可重构 FPGA 选用ALTEra 公司Cyclone II 系列中的EP2C35F672C6 芯片,片外系统主要 包括SDRAM 存储器、Flash 存储器、模数转换芯片、数模转换芯片、EPC16 增强型配置芯 片、MAX232 芯片等组成。片外系统实现数据的采集、预处理、存储和输出等功能。

2.2 控制核

在基于 FPGA 的可重构智能仪器中,EP2C35F672C6 是整个系统的核心,为了实现FPGA 与其他芯片、器件的正确通信、数据交换,需要在FPGA 上配置Nios II 软核处理器以及其 他控制器核。

(一)Nios II 嵌入式处理器的设置。首先在QUARTus II 下建立一个Project,在SOPC Builder 中选择组件列表中的Nios II Processor-Altera Corporation,考虑到芯片的性能以及资 源利用率,选择Nios II/s(标准型)CPU,在Cache & Tightly CoupLED Memories 标签下设置 Instruction Cache 为4KB。在JTAG Debug Module 标签下选择Level 3,可设置2 个硬断点、 2 个数据触发、指令跟踪和片上系统。整个Debug 模块将占用2400~2700 个LE,4 个M4K。

(二)添加SDRAM 控制器内核。在SOPC Builder 组件选择栏中选择Avalon Components→Memory→SDRAM Controller,加入SDRAM 控制器核,。在Data Width(数据 总线宽度)下拉列表框中选择16Bits,其余设置不变,因为都满足SDRAM 芯片IS42S16400 的参数要求。Timing 选项卡的参数也满足芯片要求,不必修改。

(三)添加 FLASH 控制器。在对硬件系统进行编程控制时,Flash 用于存储应用程序。 在SOPC Builder 的组件选择栏中选择Avalon Components→Bridge→Avalon Tri-State Bridge, 加入Avalon 三态总线桥; 在SOPC Builder 的组件选择栏中选择AvalonComponents→Memery→Flash Memery(Common Flash Interface),添加CFI 控制器。

( 四) 定时器设置。在SOPC Builder 组件选择栏中选择Avalon Components→Other→Interval timer,加入定时器核。定时器的硬件配置选项会影响定时器的 硬件结构,SOPC 提供了简单周期中断配置、完全功能配置和看门狗配置三种硬件配置。

(五)添加 SPI 核。采用的A/D 转换芯片和D/A 转换芯片都是基于SPI 总线进行数据 传输的,要实现Nios II 系统对转换芯片的控制必须添加SPI 核。在SOPC Builder 组件选择 栏中选择Avalon Components→CommunICation→SPI(3 Wire Serial),配置SPI 核。由于用到 的模数转换芯片AD7810 和数模转换芯片AD5611 对于Nios II 系统来说都是从SPI 器件, 所以在FPGA 中添加两个主SPI 核分别控制A/D 和D/A 转换芯片。

2.3 可重构配置文件生成

在完成可重构智能仪器的各个控制器核之后,要生成相应的配置文件,才能配置FPGA 芯片,使其实现各种功能。

配置是对 FPGA 的内容进行编程的一个过程。目前大部分FPGA 都是基于SRAM 工艺 的,而SRAM 工艺的芯片在掉电后信息就会丢失,需要外加专用配置芯片,在上电时,由 这个专用配置芯片把配置数据加载到FPGA 中,之后FPGA 就可以正常工作了。

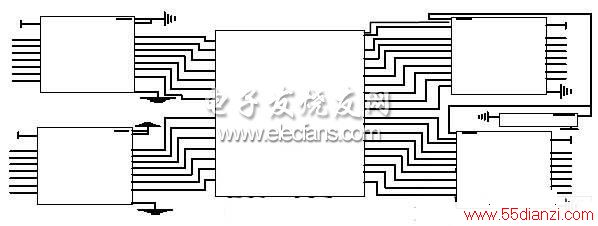

在被动模式(PS)方式下,FPGA 处于完全被动的地位。FPGA 接收配置时钟、配置命 令和配置数据,给出配置的状态信号以及配置完成指示信号等。PS 配置时序如图2 所示:

根据 SOPC Builder 中对FPGA 添加的各种控制器核,利用Quatus II 软件例化Nios II 处 理器,生成了完整的FPGA 内部顶层模块图,如图3 所示。然后利用引脚规划器PIN Planner 对其进行引脚分配。最后用进行Compilation,生成.SOF 和.pof 配置文件,完成硬件设计。

2.4 外围电路设计

外围电路设计包括存储器设计、AD 转换电路设计、DA 转换设计、显示电路设计、开 关量DI、DO 设计和RS232 通信设计等。

仪器上的存储器包含 1 片8M 字节的SDRAM 和一片32M 字节的FLASH 存储器。限于 篇幅SDRAM(IS42S16400)与EP2C35F672C6 连接的引脚、FLASH 存储器(AT49BV163) 与EP2C35F672C6 连接的引脚分配这里不再赘述。

A/D 转换电路采用了AD7810 芯片、DA 转换电路采用AD5611 芯片。

DI、DO 均为16 路,数字端口满足标准TTL 电气特性。数字量输入最低的高电平为2V, 数字量输入最高的低电平为0.8V;数字量输出最低的高电平为3.4V,数字量输出最高的低 电平为0.5V。DI、DO 部分的电路如图4 所示:

www.55dianzi.com3 可重构智能仪器软件设计

3.1 可重构仪器软件结构

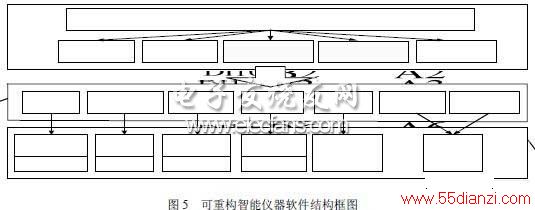

可重构智能仪器的软件结构如图 5 所示。

系统软件模块库:包含软件控制模块、RS232 通讯模块、模数转换模块、数模转换模块、 显示模块和DI、DO 开关量模块。通过软件控制模块选择其他的模块进行组合就可以实现不 同的软件功能,从而达到重构的目的。

HAL 程序库实际上包含了各种不同的硬件驱动,包括MAX232 驱动、AD 转换芯片驱 动、DA 转换芯片驱动、FPGA 的I/O 引脚驱动等。

通过选择软件模块库中的软件模块,就可以调用 HAL 程序库中相应的硬件驱动,从而 实现上层应用程序对底层硬件的控制。软件模块的可重构性对应了底层硬件的可重构性。

3.2 基于HAL 的可重构智能仪器软件开发

硬件抽象层(HAL, Hardware Abstraction Layer),是指在应用程序和系统硬件之间的一 个系统库(System Library),为嵌入式系统与硬件通信的程序提供简单的设备驱动接口。 SOPC Builder 是一个自动化的SOPC 硬件系统工具。基于HAL 的软件系统由两个Nios II 工 程所构建,用户的程序包含在一个工程中(用户应用工程),该工程依赖一个独立的系统库 工程(HAL 系统库工程)。用户应用工程包含开发的所有代码,编译该工程可以产生可执行 文件。HAL 系统库工程包含涉及处理器硬件接口的所有信息。系统库工程依赖于由SOPC Builder 产生的扩展名为.ptf 的Nios II 处理器系统。