利用 CPLD 卸载系统微 处理器 的操作任务,可延长处理器节电模式,从而显著降低 功耗

如今,降低总体系统功耗是设计便携式手持电子设备的最关键因素之一。消费者期望值的日益增长也就要求便携式设备必须延长电池寿命并提高自身性能。对于便携式系统设计人员和制造者来说,即使降低10mW 左右的功耗也是极其重要的。

如今,设计人员可以采用多种设计方法来大大降低总体系统功耗,如:

这些只是设计方法中可用来降低任意终端应用的功耗的几个例子。

其中最重要的节电技法之一是管理系统中器件操作模式的能力。如今,许多制造商提供的器件都具有节电模式,即暂时将器件从其正常操作模式挂起。这些器件如果在特定时长内不活动,可以选择关闭电源或转至非工作状态。如今的许多微处理器和微控制器都具备这种功能。通过利用和管理 PCB 上功耗大户(如处理器)的操作模式,可以显著降低系统的总体功耗。

降低功耗不仅涉及正确管理器件的操作模式,还涉及到设计能利用器件可用操作模式的系统。卸载微处理器的操作任务可使微处理器在较长时间内保持低功耗状态。降低系统功耗的一种方法是让低功耗可编程逻辑器件(如 CPLD)管理这些卸载的操作。本文讲述这种方法以及可使处理器保持较长低功耗状态的操作类型,以期降低系统功耗。

微处理器操作模式

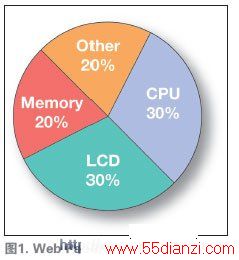

在某些便携式应用中,CPU 功耗可达总体系统功耗的 30%。图 1 所示为无线上网机应用中系统组件的典型功耗。

在正常工作状态下,微处理器的功耗范围可达 720μW 到 1W。微处理器的操作模式包括正常、运行、睡眠、挂起、待机、停止和空闲等,因器件和制造商而异。各操作模式之间的功耗变化范围可达 230mW。某些低功耗微处理器在正常操作模式下的功耗可少至 250mW。

示例

注:所提供的微处理器参考仅为示例,用来说明不同操作模式下的功耗。鉴于尚无确定功耗的标准方法,本文档中的数据以制造商提供的数据为依据,仅供参考。有关详情,请见“参考文献”。

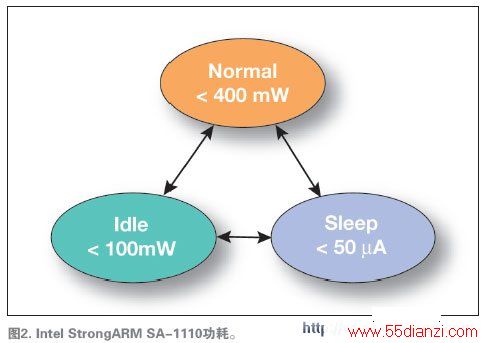

下面举例说明微处理器在不同操作模式下的功耗差异。图 2 所示为 Intel StrongARM SA-1110 微处理器在不同操作模式下的功耗。图 2 所示功耗数字的确定条件是:工作频率 206 MHz,标称外部供电电压 3.3 V,内部供电电压 1.8 V。

StrongARM 处理器的操作模式包括正常、空闲和睡眠。在正常操作模式下,CPU 满负荷运行,器件完全供电并接收有效时钟。在空闲模式下,尽管仍然为 CPU 及其他组件供电,但对 CPU 的所有时钟输入都停止,仅保持对外设的时钟输入为有效。在睡眠模式下,停止向 CPU 及外设组件供电。在睡眠模式下,除实时时钟、中断控制器、电源管理器和通用 I/O 外,所有其他功能均停止。

操作模式控制

带节电模式的微处理器具有一个板上电源管理控制器。操作模式允许操作系统或软件应用程序将 CPU 暂时挂起。微处理器执行一系列进入节电状态的指令。进入断电模式后,微处理器的若干元件仍可响应系统中断。

例如,StrongARM SA-1110 处理器的空闲模式节电效果显著,但仍保持对 LCD、存储器和 I/O 控制器等模块供电。即使对 CPU 的时钟输入已经停止,外设模块仍处于活动状态。空闲模式仍会消耗 100mW 左右的可观功率。处理器进入睡眠模式后,仅为活动模块供电,使其响应中断和唤醒信号请求。睡眠模式比空闲模式功耗更小,其所耗电流可低于 100mA。

插入响应和处理系统中断的外部器件可以减少处理器的操作任务。通过让微处理器保持尽可能长的断电模式,即可显著降低功耗。

必须发生某一事件才能使微处理器从断电模式返回到正常操作模式。以下事件可唤醒处理器,但因制造商、器件和当前操作模式而异:

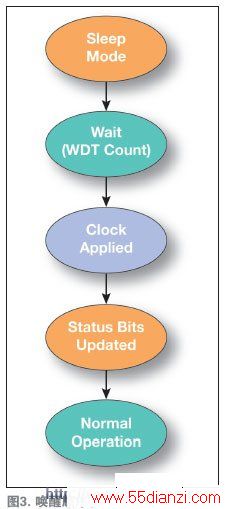

一旦识别出已启动的唤醒事件,微处理器就会开始执行从断电状态唤醒的一系列步骤。图 3 所示为处理器从断电模式苏醒的一般流程。

CPLD 设计

操作模式是在微 处理器 空闲特定时长后启用。微处理器在接收到已启动的中断时会响应该中断请求。处理器在响应中断请求时会以运行或正常模式操作。减少对处理器的中断请求数可延长处理器处于节电状态的时间。理想情况下,如果没有任何需要执行的指令,微处理器就会永远保持节电模式。插入响应和处理系统中断的外部器件可以减少处理器的操作任务。通过让微处理器保持尽可能长的断电模式,可显著降低 功耗 。

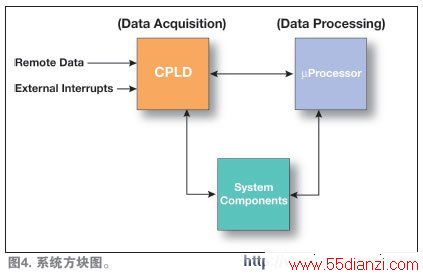

使用低功耗可编程逻辑器件来辅助微处理器可以降低系统功耗并延长系统电池寿命。业界最新的 CPLD 产品可同时实现高性能和低功耗。典型低功耗 CPLD 的待机电流小于 100μA。图 4 所示为用可再编程 CPLD 作为对输入系统中断的接口。利用外部数据采集器件卸载需要微处理器处理的中断请求可降低总体系统功耗。

系统中断

根据处理器的最终应用,有多种外部器件可以中断处理器。这些中断信号包括数据采集和数据处理两种请求。现在,通过分离对微处理器的数据处理请求,可以由外部 CPLD 来处理数据采集请求。利用 CPLD 来处理数据采集中断可以卸载对微处理器的中断请求,从而降低功耗。

是否可将数据采集中断类型划归 CPLD 取决于最终应用。可以将要求对输入数据予以响应的外设或输入数据划为数据采集中断请求类型。数据采集中断包括:

这并非可由 CPLD 处理的中断的完整列表,只是为系统设计提供一个起点。

操作流程

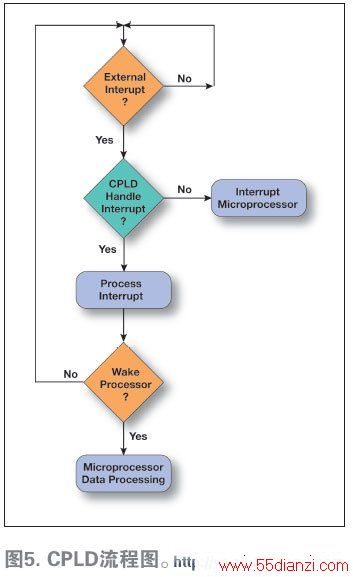

图 5 所示为 CPLD 设计的主要操作流程。CPLD 一旦识别出有效的外部中断,就会自我判断是否具有处理该中断的功能。CPLD 处理该中断之后,会向处理器发出一个中断申请,请求其进行所要求的数据处理。CPLD 如果不能处理该中断,则将其传递给处理器。CPLD 还负责监测处理器的操作状态。

功能

低功耗 CPLD 设计由处理中断请求的中断接口和控制器、处理中断的功能以及处理器接口组成。下面分别详述 CPLD 的各主要功能:

CPLD 的中断接口接收经过微处理器识别的所有外部器件的中断请求。该中断接口判断 CPLD 是否有能力处理相应的中断请求。CPLD 对请求数据接收和存储功能的数据采集中断进行处理。CPLD 如果不能处理该中断,则将其传递给微处理器。

CPLD 的中断接口为所有中断源提供屏蔽功能,并且具有判断中断源的能力。可编程逻辑能够灵活地改变触发模式,包括高低电平敏感触发模式和升降沿敏感触发模式。CPLD 的中断控制寄存器与微处理器中的寄存器相似。

中断控制器

CPLD 的中断控制器模拟系统微处理器中的功能。该中断控制器判断数据采集中断来自哪个器件,然后启动中断处理。CPLD 处理本该由微处理器处理的数据采集中断请求。

中断控制器启动处理请求的操作。由 CPLD 从远程器件接收数据的应用就是这样的例子。该器件请求将所传送的数据写入存储器。CPLD 的中断控制器识别出有效中断,然后启动存储器接口来解译数据。

外设接口

CPLD 提供处理中断请求所需的系统器件接口。所需器件接口取决于最终应用。如果外部器件向 CPLD 发出中断请求,要求对存储元件进行数据读写操作,则 CPLD 设计中就需具备该存储器的接口。所需接口类型可以为存储器接口、LCD 接口以及 PCI、UART、SPI 和 ISA 等通信接口。

本文关键字:处理器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术