采用这种模块化的设计,其光积分时间、行转移频率和像转移频率、行转移数和每行像素转移数均可调整,程序的移植性较好,可适用于不同的需要,而且也方便调试。

3 实验结果分析

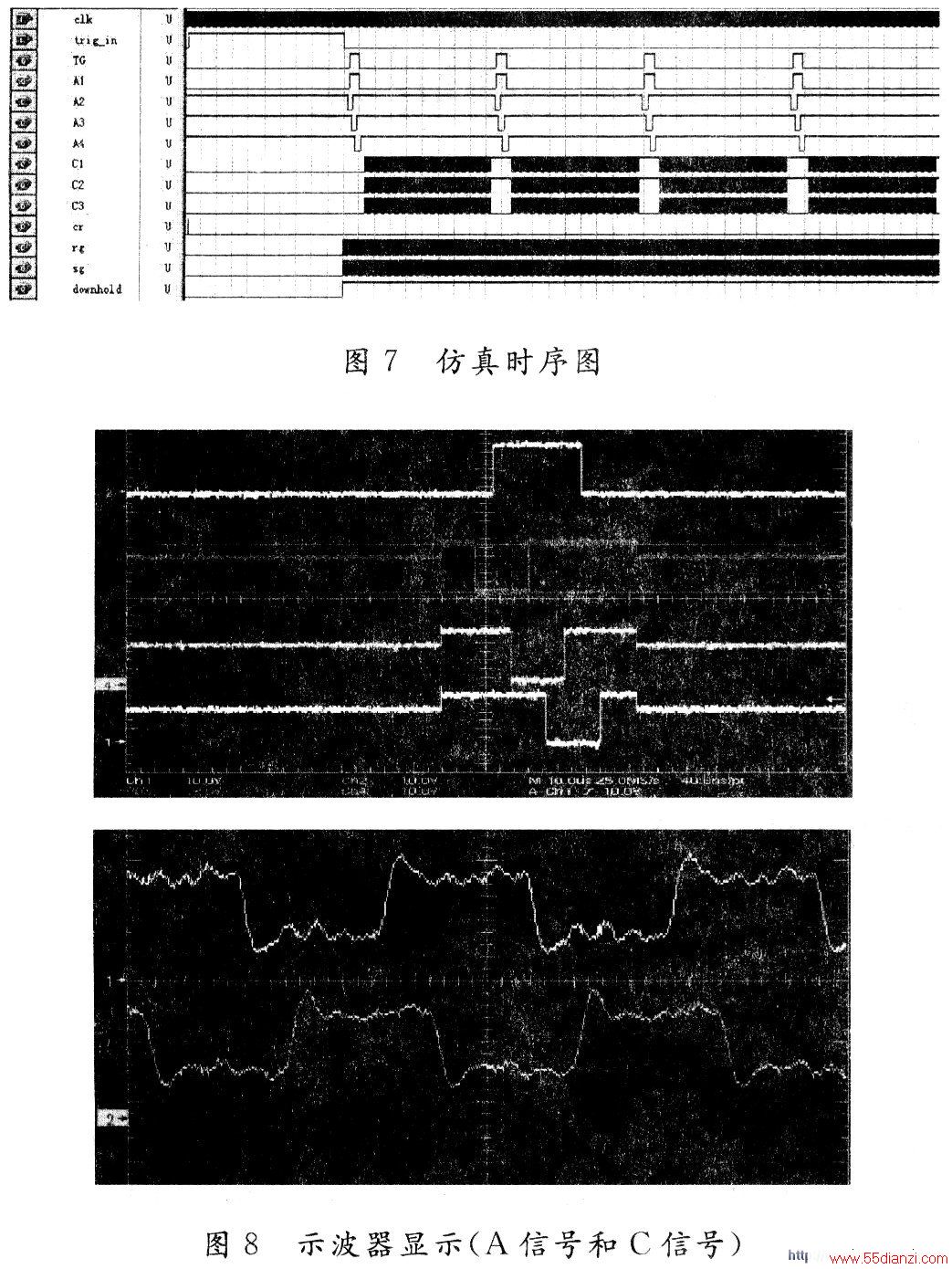

对程序进行系统仿真后的时序图如图7所示。可看出该时序符合CCD芯片的datasheet要求。将编译好的程序下载到CPLD中,通过示波器可以得到所需的驱动信号,如图8所示。

点击看原图

在实验中发现,虽然软件仿真中各个驱动信号能够严格符合CcD4052M要求的时序关系,但是实际输出到CCD信号的驱动信号却仍然有不同程度的延时。这主要是由两方面的原因引起的。首先,由于在设计初期采用的是集成开发环境下行为级的仿真功能,仿真过程不包括延时信息,只为验证代码行为的正确性,可以做到与器件无关,所以CPLD的输出会与仿真结果有所差异;其次,CCD驱动信号由CPLD产生后,需要经过后续的模拟驱动电路,由于电子器件本身的特性和差异,造成了抵达CCD管脚的驱动信号具有不同的延时。其中,第一种误差可以通过进行集成开发环境下的时序级仿真解决。这种仿真为设计的每一个底层器件加入了延时信息,可以模拟到比较接近实际电路的行为。第二种误差因电子器件本身造成的,存在个体性差异,无法进行精确的计算。解决方法是在电路设计中加入延时芯片,通过实际测量,设定不同延时芯片的延时,校正各个驱动信号间的误差。

4 结 语

该CCD驱动系统采用CPLD芯片进行设计,具有性能好,功耗低,体积小的特点。该驱动电路的研制结果表明,采用CPLD专用集成芯片进行系统设计有它自身的优点,可以简化设计,并且调试简单,可扩展性也比较强。

本文关键字:传感器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术