ժҪ�����н�����atmel��˾�ĸ�����avr ��Ƭ�� atmega103����Ҫ�����ص㣬������atmega103��fh��Ƶϵͳ�����źŴ���ģ���е�Ӧ�÷�������ϸ������Ƭ��ͬ������spi��ʹ�ü��ɣ�ͬʱ������spi��ͨ��Ӧ�ó���

�ؼ��ʣ� ��Ƭ������Ƶ��spi�������źŴ�����atmega103

��������ᣱ���� ��Ƭ�� �ǣ������칫˾�Ƴ��ľ���ָ�������㣩������������ ����㣩ϵ�е�Ƭ����Ʒ������һ����ǿ�ͣ����ṹ�������ˣ��������ģ�λ���������ýṹ����Ч֧�ָ������Լ��ܼ��ȼ���Ļ�����������

��Ƶϵͳ����裩��ָ�ز�Ƶ�ʰ�ij����Ƶͼ������Ƶ���У��ںܿ���Ƶ����Χ�������ͨ��ϵͳ�����ڸ�ϵͳ���п����š����ྶ�Ϳ�˥���Ե����������ھ��ú��������õ��˹㷺��Ӧ�á���ϵͳ�����У��źŴ���ģ����Ҫ�����Ƶģʽ����裩���й������źŵĴ�����������������롢������֯����ͬ���йصIJ����ȣ���Щ����Ŀǰ����Ƶϵͳ�Ĺؼ�����֮һ��

���Ľ��ܣ�������ᣱ���� ��Ƭ�� ���ص㼰���ڣ��ϵͳ�����źŴ���ģ���е�ʹ�÷�����ͬʱ��ϸ���ܣ���(������� ����������� �����������)���ص��Ӧ�á�

������������ᣱ���� ��Ƭ�� ����

��������ᣱ�����ǻ��ڣ���� �����ṹ�ģ����������ģ�����������������ȡ�ˣ���ϵ�м���������ϵ�� ��Ƭ�� ���ŵ㣬�������ش�Ľ������ص����£�

���ѹΪ����������������Ƶ��߿ɴ���������

����У�������ָ������ָ��ִ��ʱ��Ϊ����ʱ�����ڣ�

����У��������ֽ�Ƭ�ڿ����صģ�����洢�������鴮�����أ����������������ͣ����ֽڵ�Ƭ�ڣ����Լ������ֽڵ�Ƭ�ڣ��������

���У������ɱ�̣飯���ߡ����������ߺͣ�������ߣ�

����У�������λͨ�üĴ�����

���ں�������λ��ʱ���ͣ�������λ��ʱ����

����пɱ�̴��У�����������ӿڣ�

������ڲ��ж�Դ�ͣ����ⲿ�ж�Դ��

����У�ͨ������λ�ᣯ��ת������Ƭ��ģ��Ƚ����Լ����Ź��ȵ�·��

������߱�̡�

��������ᣱ�������������ص�ʹ���Ϊһ���ʺ��ڶ�ܡ����٣��Ҿ��и߶�����Ժ��Լ۱ȵ���������

������Ƶ�źŴ����� ��Ƭ�� ��Ҫ��

��Ƶ�źŴ���ģ���ǣ���̨�Ĺؼ�����֮һ����Ҫ������ɵ�̨��ͬ�����й����ݴ�����֯������ ��Ƭ�� �Ǹ�ģ��ĺ��ģ�ģ�������ܶ����ڵ�Ƭ����ֱ�ӻ��Ӳ�������ɵġ��ۺϿ��ǣ���Ƭ���ڸ�ģ���е����ô������£�

��������ɴ������ݽ�������Ϊ��̨�ڹ���ʱ��Ҫ���ջ��ʹ������� ��Ƭ�� �Լ�ģ���ڲ����йز������ݣ�

��������ɿ���ʵʱ�������ܣ���Ϊģ���������ϢҪ�������������������䣨������� ��� ��������Ϣ���������ݡ�ʵʱ����Ƶ�ʼ���ȡ�

�������������ݽ��������� ��Ƭ�� �ӿڡ�����䡢ͬ����Ϣ������״̬�������ݽӿڵȡ�

��������ɴ������㡣һ���̨�ڣ�蹤����ʽʱ��ÿ������Ҫ�������䡢����Ƶ�ʡ����ջ������ݵ�������֯��

������ͨ���㹻�ģ飯������ṩ���ֿ���״̬�ߣ��Թ���̨��ģ���ڲ�ʹ�á�

������ͨ��Ƭ�ڴ����������洢����ȡ��������в����Ĵ����м����ݡ�

�������˼·

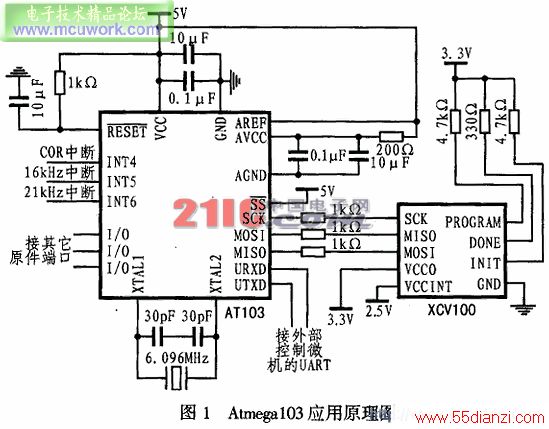

���ݵ�̨����źŴ���ģ��� ��Ƭ�� ��Ҫ�����ѡ�ã����㣵��ϵ�е�Ƭ����������ʵ�ֹ����ϱȽ����ѣ��������ٶȡ��飯��������ȣ��������������Χ��չ��·Ҳ�������ӣ��������ͨ�ſڵȣ�����ѡ�ã�������ᣱ������Ƭ�����ܽϺõ��������Ҫ����ˣ������ѡ�ã�������ᣱ������Ƭ����ʵ���źŴ���ģ��Ĺ��ܡ�ͼ����ʾ����Ӳ��ԭ��ͼ��

���⣬��ʵ��ʹ���У�����ע��������ơ�Ϊ�˱��ڵ��ԡ�ά����������չ����ϵͳ����ģ�黯������Ʒ��������ҿ��ǵ������Ŀɿ��ԣ����������ݴ���������ƣ�ͬʱ��������ݽӿڶ���ص㣬�����л�����˼�����ͨ���ԵĽӿ�ͨ��Э�顣

������������ᣱ�����ģ����ڣ���е�Ӧ��

������������֪�������������ռ����Ҫ�ĵ�λ��ģ���ڲ�����Ҫ���ƺ����ݽ�����������ɣ�������ϸ���ܣ�����ģ���е���Ʒ�����

������ ����Ĺ���ԭ��

��������ᣱ����������֮���ͨ��������и���ͬ�����ݴ��䡣���ӣ����ģ������Ӽ�ͼ����ʾ�����У�����Ϊ������ʱ������ʹӻ���ʱ�����롣������д�������������ݼĴ����IJ�������������ʱ�Ӳ���������ʱ�����ݽ��������ģ������Ƴ������Ӵӻ��ģ��������룬����һ���ֽں���ʱ��ֹͣ�������÷��ͽ�����־����ʱ��������ģ���壨�����ж�ʹ�ܣ���λ���������жϡ�ѡ��ij����Ϊ�ӻ�ʱ���ɽ��ӻ�ѡ������ˣ�����͡����ӻ�����λ�Ĵ������Կ�����һ���ֲ�ʽ�ģ��� λѭ����λ�Ĵ����������ݴ���������ӻ���ͬʱ������Ҳ���Ӵӻ������������Ӷ�����λ������ʵ�����ӻ������ݽ�����

�������Ҫ�Ĵ����������ƼĴ��������״̬�Ĵ�����������ݼĴ�����������У�����������ã�����ж�ʹ�ܡ����ݴ���˳�����ӻ�ѡ��ʱ����λ��ʱ�����ʵȣ������Ϊ�����жϱ�־�����ڱ�־д��ͻ�������Ĵ��������ڼĴ����ļ��ͣ�����λ�Ĵ���֮�䴫�����ݡ�д�üĴ���ʱ�����ȶ����ݴ��ͽ��г�ʼ�������üĴ���ʱ�������Ľ�����λ�Ĵ������ջ�������ֵ��

������ ����ij������

�ڸã���źŴ���ģ���У� ��Ƭ�� ͨ�����������ύ�����ݡ������ѡ�ã���������˾�ģ���������������������ܼ�����Ҫ���ӳ���

����������ij�ʼ��

�����ڸ�λʱ��ͨ����Ҫ�ԣ���ڽ��г�ʼ���� ��Ƭ�� ������Ϊ���������������˳��Ϊ���⣟��λ����ǰ������ʱ�ӿ���ʱΪ�͵�ƽ���ڣ�����½��ز������ݣ�ʱ��Ϊϵͳʱ�ӵģ�������������ô������ij�ʼ���������£�

������:���� ���,�磰

����� �����,��� ��;������жϱ�־��д��ͻ��־

���� ���,�磰�棷;

����� �����, ��� ��;���ã���Ĵ������

������ ����ķ��ͳ���

��Ƭ�� ÿ����Ҫ�ѣ����������������������ᣬ���Ӧ����������ġ磰���㣲���磰�������趨Ϊ��������ݻ�������Ȼ���ɣ���Ӹû�������ȡ����ֱ��������ϡ�����ķ��ͺ������£�

����_�����:���� ����,�磹

���� ����,�磰�㣲;

����� ���������,���� ;�����黺�����������ַ��Ϊ��㣲

���� ���, ���� ��;���������������������磹�㣲��ʼ�ĵ�ַ

��_��: ��� ���, ���� ��;��Ϊ������ŵĵ�ַ

��� ����, ���

��_��: ���� ���

����� ��_��

����� ���������,���� ;�����黺�����������ַ������������

���� ���,�磰��� ��;���������ı�־����ͨ������

����� �����,��� ��;�������

���� ��;���ж�

����

���Ĺؼ��֣���Ƭ�� AVR��Ƭ������Ƭ��-�����豸 - AVR��Ƭ��

��һƪ��AVR��ȷ��ʱ�ı��ʵ��