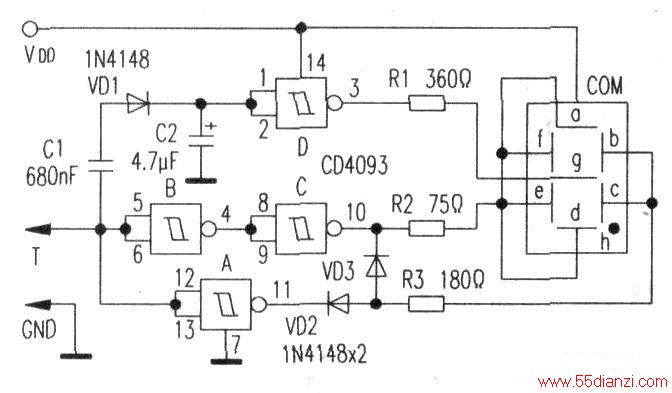

在数字集成电路系列中,逻辑门集成电路占有很大比例。利用门电路组成电平测试器.测试结果非常准确,并且电路结构简单。下图使用含有施密特触发器的二输入端四与非门CD4093和共阳极LED数码管LA3621组成的测试器电路,将四个与非门的两个输入端连在一起接成反相器,其中A检测商电平,B、C检测低电平,D检测CP时钟脉冲。Cl、VD1、C2用于时钟脉冲取样,VD2、VD3为隔离二极管,R1、R2、R3为发光笔段分组限流电阻,VDD、GND分别与被测电路的正电源和地端相连。如探针T触及高电平点,经A反相后(11)脚输出低电平,VD2导通,数码管b、c笔段发光,显示“l”,代表高电平。T输入的高电平经B、C两次反相,⑩脚输出高电平,8、d、e、f笔段反偏不会发光。同时,由于C1的隔直作用,信号不会传给D,故g笔段也不发光。如T检测到低电平,A反相后(11)脚为高电平,VD2截止。同时信号不会通过Cl,g笔段不会发光。而低电平经B、C反相后,⑩脚输出低电平,VD3导通,a~e笔段均发光,显示“0”,代表低电平。如T检测到时钟脉冲,相当于高、低电平交替输入,数码管轮流显示“l”和“0”,因时钟脉冲频率较高,两种字符合起来显示“0”。与此同时,时钟信号通过Cl后,由VD1整流和C2滤波产生高电平信号,经D反相后③脚输出低电平,g笔段发光,与前述离、低电平合起来显示的“0”重叠在一起,显示“8”字形,代表CP时钟脉冲。

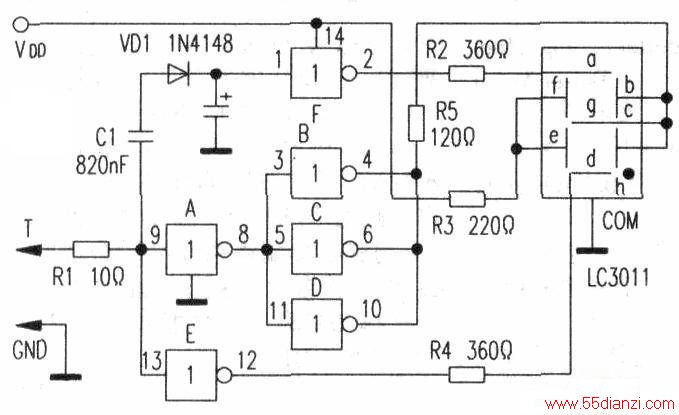

下图是使用内含施密特触发器的六非门CD40106(反相器)和共阴极数码管LC3011组成的测试器电路,其工作原理与图1基本相同。将共用发光笔段e、f,经限流电阻R3接正电源VDD,省去两只隔离二极管,只要接通电源,e、f笔段就发光。将B、C、D三个反相器并联,可增加输出驱动能力。如1检测到高电平,B、C、D的④、⑥、⑩脚为高电平,b、c、g笔段发光,与常亮的e、滗段合起来显示“H”,代表高电平。如1检测到低电平,E(12)脚为高电平,d笔段发光,与常亮的e、f笔段合为“L”,代表低电平。如1检测到时钟脉冲,则F的②脚为高电平,a笔段发光,与交替发光的“H”、“L”字形复为“8”字形,代表时钟脉冲。

分析与小结

(1)由于TTL或CMOS门电路具有确定的高、低电平输入阈值电压,因此.采用门电路设计的电平测试电路(TTL逻辑选用TTL门电路.CMOS逻辑选用CMOS门电路),不需要另外调整或设置高、低电平阐值,测量结果非常准确。

(2)采用含有施密特触发器的门电路,具有对输入信号整形作用,使输出信号的上升沿或下降沿陡直。

(3)将多余的门并接起来使用,可增加输出电流,提高负载驱动能力。

(4)使用电容C1对时钟信号取样,可以对高、低直流电平信号进行有效隔离,制作起来也比用脉冲变压器取样的方法简单。

本文关键字:门电路 电平-电压-指示电路,单元电路 - 电平-电压-指示电路