锁相环路(Phase LOCk Loop,PLL)是一种自动相位控制(APC)系统,是现代电子系统中应用广泛的一个基本部件。它的基本作用是在环路中产生一个振荡信号(有时也称本地振荡),这个信号的频率受控制电压的作用,当环路锁定时,振荡信号的输出频率与输入信号的频率完全相等,两个信号的相位差保持恒定。实现了无频率误差的信号跟踪,合理地选择PLL的直流增益、振荡频率和相应带宽可有效地改善环路性能,达到理想的效果。

l 锁相环路的组成与特性

1.1 锁相环路的组成

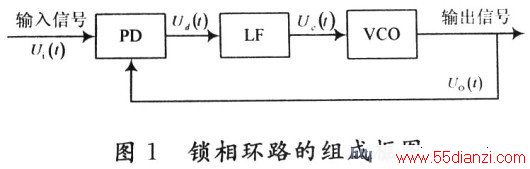

锁相环路由3部分组成:鉴相器PD(Phase Detector)、环路滤波器LF(Loop FilLTEr)和压控振荡器VCO(Voltage―ControlLED Oscillator)。组成框图如图1所示:

鉴相器PD通常鉴相器由模拟相乘器和低通滤波器组成;作用是将输入信号的相位与VCO的输出信号相位进行比较,并比较结果转化为误差电压Ud(t);该电压是两个信号相位差的函数。

环路滤波器LF 是低通滤波器,作用是滤除误差电压Ud(t)中的高频分量后得到控制电压Uc(t),并加给压控振荡器。

压控振荡器VCO 通常由变容二极管和电抗管等组成振荡电路;VCO的输出频率受Uc(t)的控制。

当输入信号和输出信号频率相同相差恒定时,鉴相器输出中的低频分量为零,环路滤波器的输出也为零,压控振荡器的振荡频率不发生变化。如果二者的频率不一致,则鉴相器将产生低频分量,并通过环路滤波器使压空振荡器的频率发生变化。环路设计得恰当,这种变化将不断使输出信号的频率与输入信号的频率趋于一致,最终二者频率相等相位差恒定,Ud(t),Uc(t)均为直流电压,VCO的输出频率将停止变化,环路处于“锁定”状态。当输入信号的频率发生变化时 (VCO的控制范围),VCO的输出就能跟上这个变化,实施跟踪和捕捉的过程,达到频率相等的要求。

1.2 锁相环路的基本特性

正常工作时锁相环路具有以下基本特性:

(1)良好的窄带特性:当环路处于锁定状态时,鉴相器输出的误差电压Ud(t)是一个能顺利通过环路滤波器的直流电压,如果此时输入信号中有干扰成分,则干扰信号与VCO的输出信号在鉴相器PD中比较所形成的误差电压受到环路滤波器的抑制(处于低通的通频带外),于是VCO的输出信号中的干扰成分大为减少,此时环路相当于一个滤除噪声的高频窄带滤波器,其通频带可以做得很窄,如在几十兆赫兹至几百兆赫兹的中心频率上实现几赫兹至几十赫兹的窄带滤波。这种窄带滤波特性是LC,RC、石英晶体等滤波器很难达到的。

(2)锁定后没有频差:在环路处于锁定状态时,环路的输出信号和输入信号的频率相等,没有剩余频差,只有剩余相位差。它比AFC系统更好地实现了频率控制,因而在自动频率控制、频率合等技术方面获得了广泛的应用。

(3)自动跟踪特性:一个已经处于锁定状态的环路,当输入信号的频率稍有变化时,VCO的频率立即发生相应的变化,使输出频率与输入频率接近并最终达到相等。有时环路虽未达到锁定状态,经过自身的调节作用可以捕捉到输入信号并最终锁定。

(4)易于集成化:组成锁相环路的基本部件都易于采用集成电路,随着集成技术的发展,整个环路包括一些放大元件、控制元件等均可集成在1块芯片上,目前常用的主要有L562,L565,L564,CD4046等集成锁相环。集成化可以减小设备体积、降低成本、提高设备的可靠性和稳定性,大大提高整机性能。

2 锁相环路的应用

由于锁相环路性能优越,现广泛用于无线电通信技术中,可实现滤波、模拟和数字信号的调制与解调、倍频、分频、混频、频率合成等方面。

2.1 锁相倍频、分频和混频

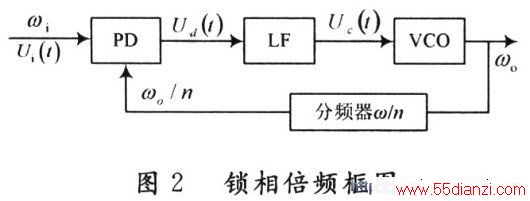

在基本锁相环路中,若将VCO的振荡频率锁定在所需要的频率上,就可进行倍频、分频和混频。

(1)倍频:在反馈环路中接入一分频器,当环路处于锁定状态时,ωi=ωo/n,输出的频率ωo=nωi为输入信号频率的n倍。如图2所示。

本文关键字:锁相环 锁相环电路,单元电路 - 锁相环电路