1 引 言

锁相环 路(PLL)是一种能够跟踪输入信号的闭环自动相位控制系统,其理论基础为自动控制理论。锁相环具有载波跟踪特性,可提取淹没在噪声之中的信号,制成高性能的调制器和解调器;用高稳定度的振荡器做参考频率,可提供一系列频率高稳定的频率源,可进行高精度的相位与频率测量等。在模拟与数字通信系统中,锁相环已成为不可缺少的基本部件。随着大规模集成电路技术的发展与成熟, CMOS 工艺以其低成本、低功耗、高集成度的优点使得采用CMOS工艺实现高性能集成锁相环具有十分重要的意义和广阔的前景。采用 电荷泵 结构的锁相环以其易于集成、低功耗、低抖动、无相差锁定等优点,得到了广泛的应用。

2 电路设计

锁相环能够实现两个电信号的相位同步、频率相同或倍频。如图1所示,锁相环由4个基本部件即鉴相器、电荷泵、低通滤波器和压控振荡器组成。鉴相器作用是对两个输入信号进行比较,输出一个正比于这两个输入信号相位差的直流电压,即一个上升或下降的脉冲信号,这个直流电压又作用于下一级电路即开关电荷泵,然后,电荷泵将鉴相器的输出信号放大,给低通滤波器的电容充放电。而环路低通滤波器是用来滤除鉴相器输出误差电压中的高频分量,起到滤波平滑作用,以保证环路稳定以及改善环路跟踪性能和噪声特性。最后,压控振荡器依据传输过来的控制电压来改变输出信号的频率和相位,因此整个系统就形成了一个反馈系统,最终压控振荡器的输出信号锁定在参考信号的频率和相位上。

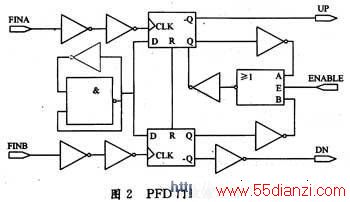

2.1 鉴频鉴相器

鉴频鉴相器是一个相位比较装置,用来检测输入信号相位与反馈信号相位之间的相位差,其结构如图2所示。PFD比较输入信号FINA和FINB的上升沿。当信号FINA的上升沿超前于信号FINB的上升沿时,PFD的输出信号UP被置为1,而输出信号DN为0,当FINB的上升沿到来时,UP变为‘0’,DN 是窄的脉冲;反之,当信号FINB的上升沿超前于信号FINA的上升沿,PFD的输出信号DN被置为‘1’,而输出信号UP保持‘0’,当FINA的上升沿到来时,DN变为‘0’,UP是一很窄的脉冲。信号UP或DN被置为高电平的时间长度等于信号FINA与FINB的相位差。当环路锁定时,PFD的输出信号都保持在低电平。

2.2 龟荷泵(CP)

在传统的电荷泵模型中,将PMOS和NMOS看作开关S1,S2,则鉴频鉴相器(PFD)的数字信号输出UP和DN可能为三种情况:

(1)状态-1:UP=0,DN=1。这时开关S1断开,S2闭合,电容进行放电,电压OUT值降低;

(2)状态0:UP=0,DN=0。这时开关S1和S2都断开,电压OUT保持为一个常量;

(3)状态1;UP=1,DN=0。这时开关S1闭合,S2断开,电容进行充电,电压OUT值提高。

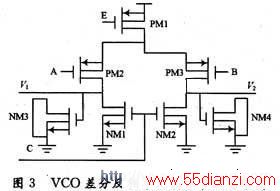

2.3 压控振荡器(VCO)

压控振荡器是锁相环的重要组成部分,很大程度上决定着锁相环的性能。它实现电压一频率的变换作用,其振荡频率受低通滤波器输出电压控制。本文研究的压控振荡器是利用电阻和电容,采用正反馈的方式来实现一种差分环形压控振荡器。此差分环形压控振荡器由五级差分电路构成,每一级的输出V1,V2接到后一级的输入 A,B,最后一级的输出与第一级的输入相连,其中两个公共端子分别为E,C。前级偏置电路受CP输出电压的控制,产生两路控制信号E,C,连接到压控振荡器的每个差分部分的控制端。这种VCO具有良好的线性调谐特性和高的输出频率稳定度的特点。

振荡器的核心部分由图3所示差分电路构成,PM1管为下端对称部分提供偏置电流,PM2,PM3起反向作用,将NM1,NM2等效为电阻,则它与相应的MOS电容连接的NM3,NM4构成了RC延迟因子,且延迟时间直接受E,C电压的控制。

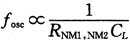

电路中的等效电阻和负载电容决定了电路的振荡频率,即 ,其中的RNM1,NM2受前级偏置部分的VE,VC控制。每一级电路所产生的输出振荡信号的摆幅为2IPM1PNM1,NM2。其中E,C二处的电压变化应当是反比例变化的,即E处电压增大引起饱和PM1管的电流IPM1减小时,C处电压须呈减小趋势以致线性等效电阻RNM1,NM2增大,以保证输出电压摆幅的基本恒定。

,其中的RNM1,NM2受前级偏置部分的VE,VC控制。每一级电路所产生的输出振荡信号的摆幅为2IPM1PNM1,NM2。其中E,C二处的电压变化应当是反比例变化的,即E处电压增大引起饱和PM1管的电流IPM1减小时,C处电压须呈减小趋势以致线性等效电阻RNM1,NM2增大,以保证输出电压摆幅的基本恒定。

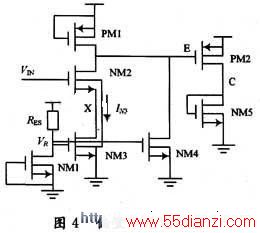

由于环路滤波器的输出电压为一个电压,要与双变量控制的VCO振荡部分连接起来,则必须要用到下面图4所示的偏置单元,将VIN单端控制电压信号转换为 E,C双端控制电压信号,实现更好的线性度和更强的电压驱动效果,减少后端振荡部分随时间的能量衰减。

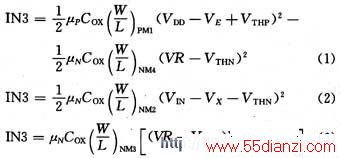

由图可知,RES的电阻值和NM1的尺寸决定了NM3,NM4的栅极电压,NM4的漏极连接到PM1的漏极,此处的电压由PM1的漏电流决定,而此漏电流等于流过NM3,NM4两管的电流之和,而这两管的电流又由VIN和E处的电压来决定。由此相互制约的关系,可以列出关于E点电压VE,流过NM3的漏极电流IN3以及NM2漏级电压VX的关系方程如下:

由上述三元三次方程即可解出E处电压值。C处电压完全由VE和PM2,NM5的相对尺寸所决定。

2.4 环路滤波器

环路滤波器具有低通特性,在 锁相环 中起到低通滤波的作用,而且它对整个环路系统的参数设计起着决定性的作用。本设计采用二阶无源低通滤波器,详见文献[3]所述。

本系统所设计的锁相环可广泛应用于电源电压为5 V时,锁相环捕捉带为41~110 MHz,3 V时捕捉带则为25~58 MHz。由文献[5]中所述,该系统采取的是电压型 电荷泵 ,将电压型转换为电流型,查出内部MOS饱和导通,保证UP和DN为恒压源的最大导通电流,可得 R1。以电源电压为5 V,忽略分频环节为例,可以得到:

3 仿真结果

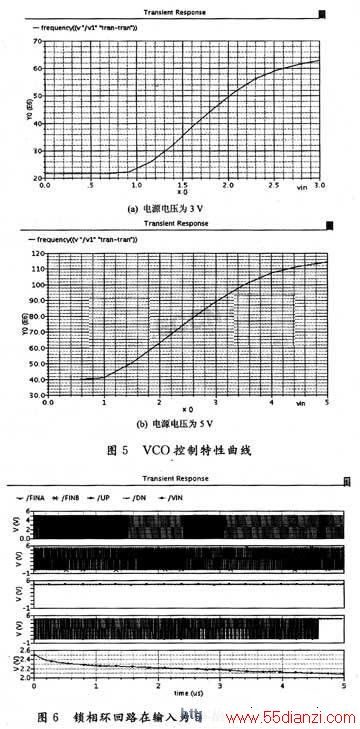

采用0.5μm工艺库,Cadence SpeCTRe工具对本文所设计的锁相环设计可以得到下列结果:

图5(a)是电源电压为3 V时的VCO控制特性曲线,有效工作范围为25~58 MHz,且线性度良好;图5(b)是电源电压为5 V时的VCO控制特性曲线,有效工作范围为41~110 MHz,且线性度良好。

另外通过对VCO起振过程的测量可知,起振时间很小,为63.5 ns。

图6是 锁相环 回路在输入为50 MHz时的输出响应,锁定时间约为4.6μs。

4 结语

使用0.5 μm CMOS 工艺实现5 V锁定范围为41~110 MHz,3 V时锁定范围为25~58 MHz的锁相环单片集成电路,经过分部仿真和总体系统仿真可知,运用本文所述方法设计二阶三型锁相环芯片各组成部分特性与理论相符,可以实现相位和频率的同步跟踪,且时域特性良好。

本文关键字:锁相环 锁相环电路,单元电路 - 锁相环电路

上一篇:高频锁相环的可测性设计