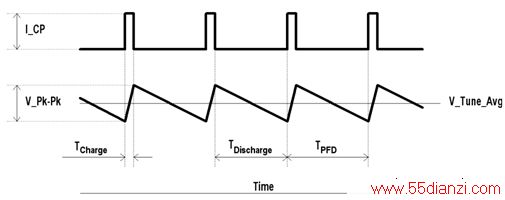

图 6:CP 通过 I_Leakage 放电,每 PFD 周期再通过 ICP_UP 充电

要推导所得杂散噪声,需要对环路稳定性的要求有所了解,首先是 LBW 限制。PLL 系统的 LBW 设计为至少比 FPFD 少 10 倍:

这意味着,PFD 周期为:

为了建立具有大量相位裕度的稳定环路,在环路中插入一个由图 5 中 RZ 和 CI 组成的零点,位置大约在 1/3 LBW 处。

在最后一个等式中用 TPFD 替代 LBW,产生

这意味着,PFD 周期几乎是比零点τZ 时间常数短 5 倍。这表明,在一个 TPFD 周期中 CP 两端产生的纹波大多不会被 CI 看到。闭环带宽 LBW 近似等于开环增益的单位增益交叉点 (unity crossing)。既然该零点位于环路带宽之内 (位于开环增益单位增益交叉点的 1/3 处),那么 CI 两端的电压由负反馈决定,而且在大多数情况下等于 DC 值。

实事求是地讲,在图 6 所示的 PFD 周期中,仅 CP 在放电和充电。

如果用一个恒定电流源 I 给电容器 C 充电和放电,那么经过一段给定的时间ΔT,该电容器两端的电压由以下等式给出:

为了在 LO 端保持固定输出频率,图 6 中放电周期发生的电压下降等于充电周期的电压上升。也就是:

其中,TCharge 是充电泵电流在每个 PFD 周期工作的时间。

充电泵电流 I_CP 的大小通常在 mA 范围,I_Leakage 的大小通常在 nA 范围,这意味着:

这表明,CP 两端的纹波电压可以用锯齿波表示。

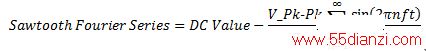

为了研究这种锯齿波对 LO 信号频谱的影响,而且既然该波形是一种周期函数,那么该锯齿波可以用傅立叶级数 (Fourier Series) 分析分解成其频率分量:

其中:

其中 n = 1,基频峰值为:

二阶谐波峰值为:

等等。

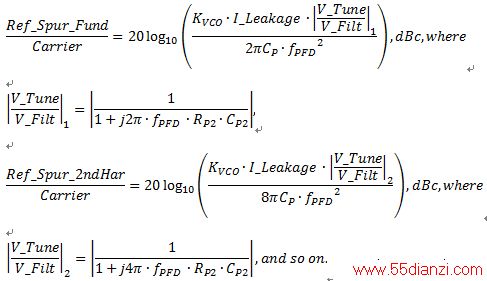

在图 6 中等于 V_Tune_Avg 的 DC 值按照所要求的 LO 频率由负反馈设定。然而,AC 组件通过 VCO 的调谐引脚对 VCO 进行频率调制,调谐灵敏度为 KVCO,结果产生了以 fPFD 为基频的双边带杂散噪声。附录导出了以下等式,稍后会用到这个等式。

www.55dianzi.com

因为 FPFD 是基频和最低频率分量,按照设计,至少比开环增益的 0dB 交叉点高 10 倍。在这些 AC 分量的负反馈影响是微不足道。

为了算出基频基准杂散噪声与载波的功率比,设 FM = fPFD、Em = Vpk-Fund 和

就二阶谐波基准杂散噪声而言,fm = 2 fPFD、Em = Vpk-2ndHar 且

用类似方法可以算出针对较高阶谐波的比值。

有源环路滤波器举例

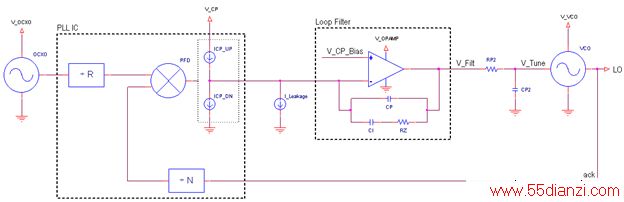

图 7 显示了一个围绕运放建立的有源环路滤波器例子。I_Leakage 表示充电泵和运放的泄露电流之和。既然环路滤波器具有类似的结构,所以这里运用了与无源滤波器例子中相同的方法。在运放的输出端增加由 RP2 和 CP2 组成的极点,以将该器件的噪声贡献限制在LBW 的 15 或 20 倍以外,这可降低 VCO 调谐节点处的锯齿波信号幅度。应该提到的是,CP2 包括 VCO 调谐端口的输入电容。

图 7: 采用有源环路滤波器的 PLL 系统,I_Leakage 代表充电泵和运算放大器的泄漏电流

锯齿波信号经过低通滤波,低通滤波的等式可以用拉普拉斯变换域 (LaplaceTransforma domain) 的基本分压等式得出,并可表示为:

其中 f 代表频率,单位为 Hz。

锯齿波信号的傅立叶级数分量自然会根据其频率不同而受到不同的影响。基准杂散噪声与载波之比变为:

该理论的实验室验证

我们在实验室中再现了图 5 和图 7 所示的 PLL 系统。用一个精确的电源仪表在充电泵节点处引入外部电流,以清除由系统固有泄漏引起的内在基频基准杂散噪声。然后,额外给环路注入特定大小的电流,同时测量基频基准杂散噪声的大小。图 8 比较了对两种类型的滤波器所测得和所计算的值。在仪器准确度和组件容限范围内,所测得和所计算的数字是一致的。

本文关键字:暂无联系方式锁相环电路,单元电路 - 锁相环电路

上一篇:改进型CMOS电荷泵锁相环电路