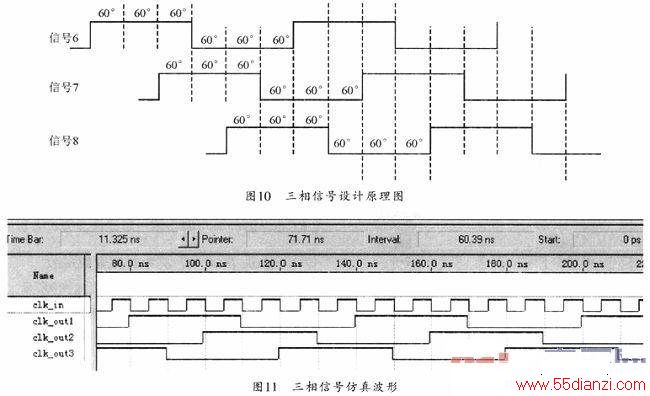

从图10可以看出将品振基准频率16.384MHz进行2371次分频看得到6 kHz作为移相输入频率,移相间隔为1 kHz,在1个计数周期T即6 kHz内,信号6~信号8对应逻辑电平输出见表1。

电路仿真波形如图11所示,实验波形见图7。

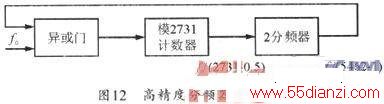

3.3 高精度分频器设计

电路信号输出精度要求小于10-3,信号1~信号5均为基准频率的整数倍分频精度均有满足要求,信号6~信号8采用整数倍2731次分频精度可达1.2x10-4,虽也满足指标要求,但在高温和低温情况下随着基准频率的温漂精度出现了临界情况。为了有效解决1 kHz频率精度的问题,需要设计高精度的分频器,设计了2730.5次分频,电路结构框图如图12所示。

从图12可看出将基准频率分频2730.5次得到6.000366 kHz经过相移电路可以得到三相信号频率为1.000061 kHz,频率精度为6.1× 10-5。由上可以看出,设计半整数分频器比整数分频器得到的信号频率精度高出一个数量级,实验证明在高低温情况下,电特性完全满足指标要求。

4 结束语

本电路采用一片CPLD (16×16 mm)实现了2730.5分频器、32分频器、三个16位计数器、一个6分频器、一个逻辑分配器的功能,只占用了该芯片69%的逻辑资源和36%的输入/输出口(I/O口)。

本文详细阐述了交流电源信号发生器的工作原理及其在系统中的功能,介绍了常规的信号发生装置的设计方法,并比较了其优劣势。采用可编程逻辑器件设计了交流电源信号发生器,这种新型方法具有信号输出精度高、抗干扰能力强、体积小、设计修改方便、成本较低等优势,为其他相似电路的设计提供了参考。