……

图5 改进后的状态机综合后的波形

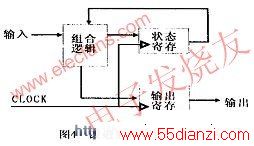

显然这种结构的状态机稳定性优于一般结构的状态机,但是它占用的逻辑资源更多,电路的速度可能下降,在设计时应综合考虑.

另外,为防止电路进入非法状态,可以设计成自启动结构,在VHDL描述的状态机中添加一个“when others”语句是行之有效的.

3 选择不同编码方式、不同结构的状态机的技巧

3.1 针对不同结构器件选择不同编码风格

基于乘积项结构的CPLD器件适合于设计全编码状态机,在全编码状态机中采用格雷码表示状态值.这对于逻辑资源较少的器件是一种不错的优化方法.

基于查找表结构的FPGA器件适合于设计成“ONEHOT”方式编码的状态机,这种结构状态机只用一位二进制数表示一个状态,可提高稳定性,但要占用更多的逻辑资源.

3.2 根据逻辑资源大小选择状态机结构

当设计的状态机状态转换次序出现多路径时,采用格雷码表示状态值不会有任何作用,因为此时有些相邻状态不只是一位不同.在逻辑资源允许的情况下,可以考虑在状态机后级增加一级输出寄存器,可确保输出不产生毛刺,使状态机输出稳定可靠的信号.

本文关键字:稳定性 嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术