摘 要 在片上可重构系统(Reconfigurable System 0n Programmable Chip)上,通过分析软/硬件任务的特点,扩展μC/OS―II对硬件任务的支持,提出一种基于统一优先级调度的分层的软/硬件任务通信结构,并在此结构上实现软/硬件任务间的消息队列通信。最后,通过模拟实验证明其有效性。

关键词 可重构系统 μC/0S―II 消息队列 软/硬任务间通信

引 言

目前,在面向应用的嵌入式体系结构的研究中,为了能同时利用通用处理器(CPU)的灵活性和专用集成电路(ASIC)的高效性,一些研究者将系统中性能要求较高的模块用FPGA等可编程器件实现,与通用处理器集成可重构片上系统。随着现场可编程门阵列(FPGA)技术的.快速发展,可重构技术开始受到研究者们越来越多的关注。但是可重构计算的发展现状是硬件远远领先于软件,在可重构计算中需要一个操作系统来管理新的可重构硬件资源,屏蔽硬件细节,并向开发人员提供高层次的编程模型。因此一些研究者将由可编程器件实现的任务模块抽象为硬件任务,并纳入可重构实时操作系统的统一管理,由可重构实时操作系统负责任务调度、系统资源管理以及任务间的通信和同步等工作。

迄今,对可重构系统任务间通信的研究取得了一些成果。例如,Miljan Vuletic等人在参考文献中将纯软件任务环境的虚拟存储访问向可重构环境进行了扩展,以方便应用编程和移植;Philip Garcia等人在参考文献中对硬件任务接口进行了研究,以实现对硬件任务的统一封装。但这些研究仅着眼于底层数据的交互,而没有考虑通信中伴随的上层任务间的同步和互斥逻辑;另外,张磊等人在参考文献中对软/硬件任务互斥进行了研究,但没有考虑大量数据跨越CPU和FPGA边界的情况。因此,本文在这些研究成果的基础上,结合底层实现和上层逻辑对基于统一优先级调度的可重构系统中软/硬件任务间通信进行探讨。

1 可重构系统中软/硬件任务间通信分析

1.1 相关概念

硬件任务,是指由可重构硬件资源实现的功能模块,相对于软件任务具有以下特点:

①硬件任务的数量受限于可重构资源的数量;

②硬件任务可以实现微观并行;

③硬件任务通过配置可重构资源来建立,建立时间长,不可以忽略不计;

④由于硬件任务在运行的切换开销较大,因此不必像软件任务那样进行切换来分享CPU,而是可以独享相应的资源。

为了支持统一优先级调度,软/硬件任务可统一表示为Ti(ai,ei,di,ci,wi,hi)。其中,ai表示任务到达时间,ei表示任务最坏运行时间,di表示任务完成截止时间,ci表示任务配置时间,wi和hi表示硬件任务的宽度和高度。由于硬件任务和软件任务具有不同的特点,从而可将其中任务间的通信和同步分为3类,即软件任务(SWT)之间、软/硬件任务之间以及硬件任务(HWT)之间。

1.2 分层的通信模型

对于任何一个操作系统来说,任务间的通信和同步都是必不可少的。系统中各任务的运行不仅与任务的应用逻辑相关还与系统的状态相关,而系统的状态又由系统中运行的多个任务决定,因此任务间的通信往往伴随着同步和互斥的实现。为了便于任务间的通信,从传统纯软件任务环境向可重构环境的扩展,将其分为逻辑机制和物理实现两个层次。其中逻辑层主要负责多个任务间同步控制以及数据的保护,与底层的数据交互无关;而物理层则负责底层数据交互的实现,即逻辑层和物理层以松耦合的方式组合,从而方便了系统的移植和通信机制的扩展。

就逻辑机制层而言,在传统的纯软件任务的环境中,运行于CPU上的多个软件任务具有宏观上并行微观上串行的特点,操作系统在对这些任务的资源共享和数据交互的管理上已有信号量、互斥量、消息队列等成熟的通信机制。但在可重构系统中,软件任务和硬件任务分别运行于CPU和FPGA上,软/硬件任务间及硬件任务间具有微观并行性,因此需要扩展这些通信机制对硬件任务的支持,以实现跨越CPU和FPGA边界的软/硬件任务间通信。这主要表现在针对不同类型的任务采取不同的后续措施上,同时向上层应用提供统一的通信接口。

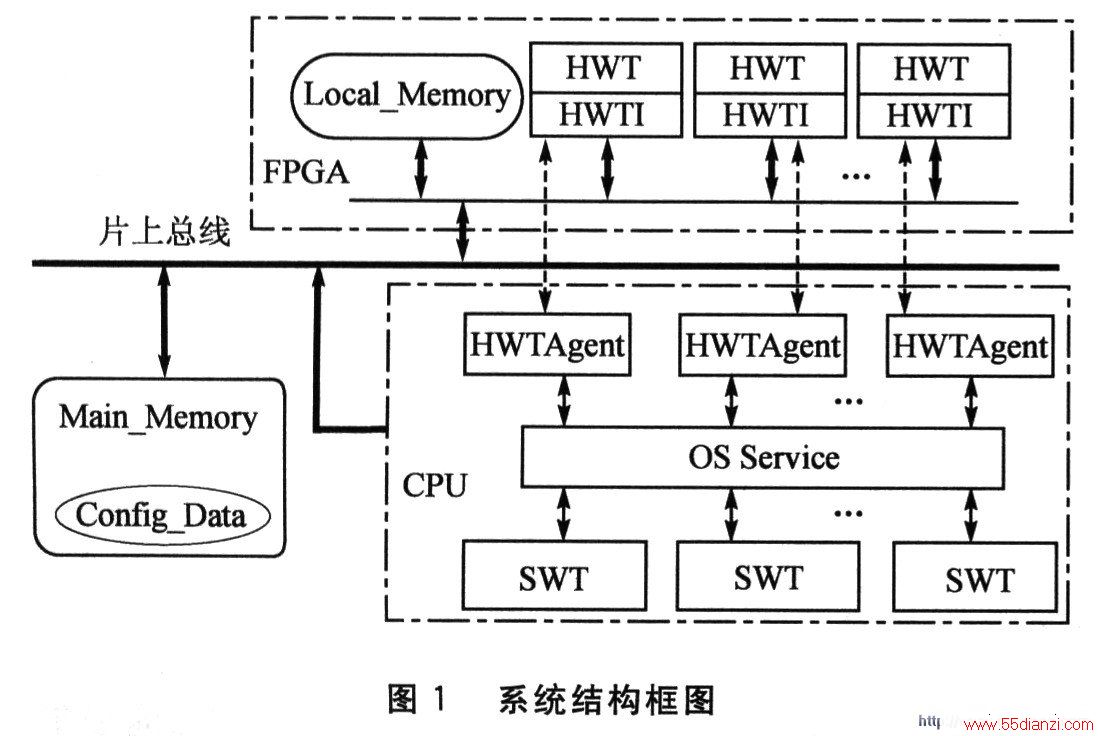

而对于物理层的实现,考虑到分布式存储中消息传递方式实现的通信开销较大且实现复杂,采用图1所示的系统结构。CPU、FPGA以及系统主存挂接到总线上组成RSOPC。CPU除运行一定的用户软件任务之外,还负责提供操作系统服务,包括任务调度、资源管理、通信和同步管理等。操作系统通过统一的软/硬件任务视图――任务控制块来对各个任务进行管理。硬件任务(HWT)运行于FPGA上,并由FPGA给每个硬件任务提供一个统一的硬件任务接口(HTI)供操作系统和硬件任务的交互,同时每个硬件任务在CPU上有代理任务与其对应。而软件任务的代码和数据以及硬件任务的配置数据都存放于系统内存中,CPU通过片上总线读取存储器中的硬件任务配置数据对FPGA进行配置。