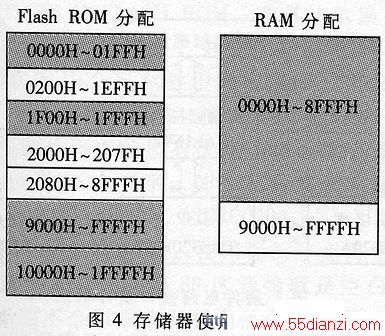

图4中白色区域是单片机通过总线直接寻址的区域,可以由单片机直接进行访问。灰色区域为内存的扩展区域,不能被单片机直接访问,但可以通过前面介绍的方法由EPLD生成地址进行读写操作。下面简要介绍一下各个区域在实际中的用途:Flash ROM中的0000H~1FFH和1F00H~1FFFH因为容量很小,没有被利用。系统启动后从Flash ROM的2080H处开始执行程序,将2000H~8FFFH的内容复制到RAM中的9000H~FFFFH,然后跳转到RAM中执行系统程序。由于Hash ROM的速度慢,需要在读写过程中插入一定量的等待周期,因此将程序复制到RAM中执行可以提高系统的性能;同时系统在对Flash ROM进行写入操作后,编程阶段的10ms内不能对其进行读取,因此RAM在这个时候也提供了程序运行的位置。这样分配后,程序的长度被限制在28K字节,实际中这个数量完全可以满足系统的需求。

Hash ROM中的9000~FFFFH共28K字节,用来保存4段系统运行配置程序,每段长度可达7K字节;10000H-1FFFFH共64K字节,用来作为采集数据的保存区域。RAM中的0000H~8FFFH共36K字节,用来作为数据的缓存区域。从上面的分析可以看出,最终设计的各项指标都已经超过实际的需求,能很好地解决实际应用问题。

4 合理利用日EADY信号

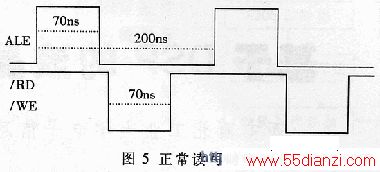

最后介绍一下单片机就绪信号READY在这个系统中的关键作用。从前面的设计中可以看出系统存在着高速RAM和慢速Hash ROM存储器,开始时,Hash ROM选用了AT29C1024-70JCt31,它是该型号中速度最快的,有效数据建立时间仅为70ns。单片机不插入等待周期的读写时序,如图5所示。

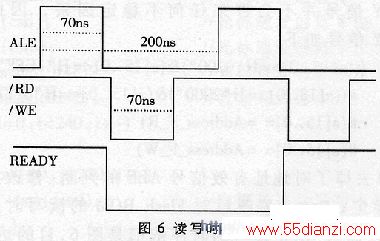

从ALE下降沿地址有效到/RD上升沿的时间是80ns,Hash的响应时间为70ns,再加上EPLD的延时就造成了单片机从Hash ROM读取数据的不稳定,表现在无法对Flash ROM进行在线写入、经常发生错误的执行结果、死机等。为此必须加入等待周期,延长读、写时间才能满足Hash ROM的要求。在这里只需插入一个等待周期(100ns)便可以满足要求,因此设置芯片配置字节CCR.5=0,CCR.4;0[1]。这样,当READY信号为低电平时便自动插入且仅插入一个等待周期。一个简单的做法就是把Flash ROM的片选信号/CS2连接到READY,这样,当选中Flash ROM芯片时READY信号就跟随/CS2同时变为低电平。按照这样的设想可在EPLD内部重新设置READY信号,描述如下:

ready=!(((a[15..0]>=H"0200")&(a [15..0]<:=H"1EFF"))

#((a[15..0]>=H"2000")&(a[15..0]<=H"8FFF"))

#(a[15..0]= =Address_F_R)

#(a[15..0]= =Address_F_W)&! ALE)

可是实际故障依旧,通过测试得到的时序信号如图6所示。

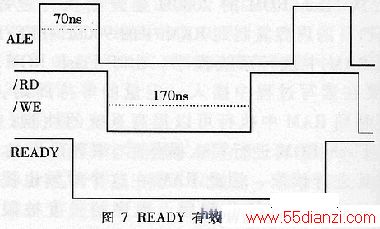

READY信号的产生落后ALE下降沿5ns,造成READY信号产生无效,解决这个问题的唯一方法是提前生成READY信号。实际中有效地址是在ALE下降沿锁存后产生的,这也是READY信号产生表达式中最后一项的来源,但是考虑到地址的产生应该发生在ALE下降沿之前,以保证锁存到正确的地址。因此大胆设想让READY信号的产生不再受ALE的控制,只要总线上产生地址就可以作出判断,从而提前生成READY信号。但这样的做法破坏了同步时序

,而且异步生成READY信号容易产生冒险现象。通过分析,可以发现异步生成READY信号并不会带来任何不稳定因素,因此修改READY信号如下:

ready=!(((a[15..0]>=H"0200")&(a[15..0]<=H"1EFF"))

#((a[15..0]>=H"2000")&(a[15..0]<=H"8FFF"))

#(a[15..0)= =Address_F_R)

#(a[15..0]= =Address_F_W)

即去掉了对地址有效信号ALE的判断。修改后系统工作稳定、正常。修改后对Hash ROM的读写时序如图7所示,而对RAM读写的时序依旧是图6,目的达到。考虑到插入一个等待周期后大大增加了读写时间,因此将AT29C1024-70JC换成廉价的AT29C1024-12JC(有效数据建立时间为120ns)[3],系统依然能够稳定工作。通过使用,证明这种存储器设计方案是可行的。

前面详细地介绍了一种实用的存储器扩展方法,该方法是基于PLD器件实现的,有效地解决了嵌入式系统,尤其是数据采集、存储系统中内存扩展的问题。该方法能够简化程序设计,并且不需要随CPU型号的变化而修改设计,具有很好的可移植性。同时还给出了一种较为复杂的单片机外部存储器的组织方案,包括了FLASH ROM和RAM构成的存储系统。最后提出了将READY信号由同步产生改为异步产生的方式,解决了CPU在高速RAM与低速Flash ROM之间切换产生的问题,最终设计成了一套较为完善的CPU外部存储器系统。

本文关键字:嵌入式 嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术