һ�� PIC16F87X���ж�Դ

����PICϵ�е�Ƭ���ǵ��������Ϻ���Ӱ�����ľ���ָ���RISC�������������зḻ���жϹ��ܡ����й���ǿ����С��ߵ��ͺŵ��ж�Դ��18��֮�ࡣ��PIC��Ƭ�������У���λ��������ˮƽ��PIC16F87X��ϵ�е�Ƭ���߱����ж�Դ���14�֡����У���Ƭ�����ͺŲ�ͬ���ж�Դ�����ࡢ����Ҳ��ͬ�����1���С��䲻��֮���ǣ��ж�ʸ��ֻ��1�������Ҹ����ж�Դ֮��Ҳû�����ȼ���֮�֣����߱��������жϡ�

�����ӱ�1�п��Կ��������ж�Դ�����϶����������Χ�豸ģ�����Ӧ�ġ����У�������Χ�豸ģ���Ӧ��1���ж�Դ�����綨ʱ��/������TMR0ģ�飩���е���Χ�豸ģ���Ӧ��2���ж�Դ������ͨ��ͬ��/����/������SCIģ�飩��Ҳ�е���Χ�豸ģ��û���ж�Դ��֮��Ӧ����������/����˿�RA��RCģ�飩�����е��ж�Դû����Χ�豸ģ����֮��Ӧ�������ⲿ�����ж�ԴINT����

���� PIC16F87X���ж�Ӳ����

������PIC16F87X����ϵ���У������ͺŲ�ͬ���ж�����·Ҳ�����Ų��죬�ж�Դ���������Ҳ��ͬ�����ľ߱�14���ж�Դ�����ٵľ߱�10���ж�Դ�������1�������в��ж˿�ģ��Ͳ��ж˿��ж�Դ��ֻ��40�ŷ�װ���ͺţ�PIC16F871��PIC16F874��PIC16F877���Ż�߱���������28�ŷ�װ���ͺţ�PIC16F870��PIC16F872��PIC16F873��PIC16F876���߱���

����PIC16F87Xϵ�е�Ƭ���ж�ϵͳ������·��ͼ1��ʾ��ÿһ���ж�Դ��Ӧ��1���жϱ�־λ����ΪXXXF��F��Flag�ĵ�1��Ӣ����ĸ����1���ж�����λ���߽��ж�ʹ��λ����ΪXXXE��E��Enable�ĵ�1��Ӣ����ĸ�����ж�Դ�������жϱ�־�ź��Ƿ������ǰ���ݣ����ܿ��ڶ�Ӧ���ж�����λ��ÿһ���жϱ�־λ����Ӧ��1�������������ж�Դ����CPU�ж�ʱ����֮��Ӧ�Ĵ���������Ӳ���Զ���λ�����ô����������������û����ų�����ʵ�ֵģ�ÿһ���ж�����λҲ��Ӧ��1�����������ô���������λ������������û�������ɵġ�

����ͼ1��������·��1���ɼ��ŵ�·���ɵ��������·����ȫ��14���ж�Դ��2���ݶӲ����ſ�����1�ݶ���ֻ������3���ж�Դ��������ж�Դȫ�����ŵ���2�ݶ��С���������Ϊ�������ڵ�PICϵ�е�Ƭ���ͺ�����ݣ�ǰЩ�����Ƴ��ĵ�Ƭ���ͺ�Ƭ�����õ���Χ�豸ģ���������٣���Ӧ���ж�Դ��������ȻҲ���٣�����PIC16C61ֻ�е�1�ݶ��е�3���ж�Դ�����������Ƶ�һЩPIC��Ƭ�����ͺ�����ԭ�еĵ�Ƭ��оƬ����֮�Ͻ���һЩ������չ�������ġ�

ͼ1�ж���

www.55dianzi.com

�������е� �ж� Դ����ȫ���ж�����λ��Ҳ���Գ�Ϊ������λ��GIE�Ŀ��ơ���1�ݶӵ��ж�Դ������ȫ���ж�����λ�Ŀ��ƣ���Ҫ�ܸ����ж�����λ�Ŀ��ƣ���2�ݶӵ��ж�Դ�����ܵ�ȫ���ж�����λ�����ж�����λ�Ŀ��ƣ���Ҫ�����ܵ�1�������ж�����λPEIE�Ŀ��ơ�

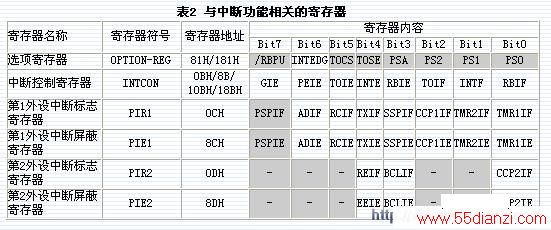

���� �ж���صļĴ���

�������жϹ����йص�����ܼĴ�������5�����жϿ��ƼĴ���INTCON����1��Χ�豸�жϱ�־�Ĵ���PIR1����1��Χ�豸�ж����μĴ������ֳ��ж�ʹ�ܼĴ�����PIE1����2��Χ�豸�жϱ�־�Ĵ���PIR2�͵�2��Χ�豸�ж����μĴ���PIE2�����2���У�5���Ĵ����й���40λ������ʹ����30λ���ֱ���ͼ1�е��ж�����·���������źų��ϸ��Ӧ��ϵ��Ҳ��������ʽ���ϸ��Ӧ��ϵ����5���Ĵ�����������RAM���ݴ洢����ͳһ����ĵ�ַ��Ҳ����˵��PIC ��Ƭ�� ������5������Ĵ���������ͨ�Ĵ�����Ԫ�����ʣ���������д������������������ڼ���ָ���ָ�����ͺ�ָ��������Ҳ����ѧϰ������ͱ�̡�

�ġ� �жϵĴ���

������Ƭ����λ����Ӳ���Զ���ȫ���ж�����λ��������GIE=0�����������е��ж�Դ���жϷ���ָ�RETFIE��ִ�к�Ҳ��Ӳ���Զ���������λ��������GIE=1�����¿������е��ж�Դ�����۸����ж�����λ��ȫ���ж�����λGIE���ں���״̬���ǿ��Ż��ǽ�ֹ������ijһ�ж�Դ���ж���������ʱ�����ᷢ���ж�������Ӧ���жϱ�־λ���ᱻ��λ��=1�������ǣ��Ƿ��ܹ��õ�CPU����Ӧ����Ҫ���ݸ��ж�Դ���漰�����ж�����λ��״̬������CPU��Ӧ�жϺ���Ӳ���Զ���ȫ���ж�����λ�������㣨GIE=0�����������е��ж�Դ�����ⷢ���ظ��ж���Ӧ��Ȼ����Ӳ���Զ��ѵ�ǰ�ij��������PCֵ��������ϵ��ַ��ѹ���ջ��ʵ��ΪӲ����ջ�������Ұ�PC�Ĵ��������ж�������ַ��0004H�����Ӷ�ת��ʼִ���жϷ���������жϷ����������б��밲��ָ���鷢��������ж�Դ�����ͬʱ���Ŷ���ж�Դ�Ļ����������ͨ���������ж�Դ�ı�־λ��ʵ�֡�һ��ȷ��������������ж�Դ�����������Ѹ��ж�Դ�ı�־λ��Ϊ�����㣬����ִ���жϷ���ָ�RETFIE�����ؿ��жϺ������жϱ�־λ��Ϊ��1��������CPU�ظ���Ӧͬһ���ж������жϷ�������ĩβ�������1���жϷ���ָ�RETFIE����ִ�и���ָ����������ؿ��жϣ����һ�������Ӳ���Զ��������ڶ�ջ�����Ķϵ��ַ���������Żص����������PC�У�ʹCPU���غͼ���ִ�б��жϵ�������

����1�� �жϵ���ʱ��Ӧ����ʱ����

����1���жϹ��̣����ж�Դ�������õ�CPU����Ӧ��Ȼ����һ�����ӳ�ʱ�䡣��������źŵ�ʱ��ͼ��ͼ2��ʾ��

ͼ2INT�����ж�ʱ��ͼ

������ͼ2�У���1����ϵͳʱ�������źţ�ÿ4��ʱ�����ڶ�Ӧ1��ָ�����ڡ���2�о���ָ�������źš����ź�ֻ����RC��ģʽ�£���OSC2���Ͽ�����Ƭ���ͳ�����3���ǵ�Ƭ���ⲿ����INT������ж������źš��ⲿ�ж��ź�INT���ñ��ش����ġ�����Ԥ���趨����INT�ж��ź���������Ч�Ļ�������źŵ������ؽ�����1��ʱ�����ں������жϱ�־λINTF����λ����4�д���INTF�źš�ÿ��ָ�������ڵĵ�2��ʱ������������ʱ�����źű����1�Ρ�һ����INTF�źű�����Ϊ��1������CPU���ڽ�������1��ָ�������ڣ���ȫ���ж�����λGIE���㡣��5����ȫ���ж�����λGIE����GIE�źű��������һ��ָ�������ڣ����������PC�������ж�����0004H����ͼ2�е�6�С�ͬʱ�ڸ�ָ����������ɵ��жϷ���������ת������ʵ����ȡ���ӳ��������ָ���ָ�0004H������ͼ2�е�7�С�������1��ָ�������ڣ���ʽ��ʼִ���жϷ������ĵ�1��ָ���ͼ2�е�8�С���INT����������Ч�źţ����жϷ������ĵ�1��ָ��õ�ִ�У���Լ��Ҫ3��4��ָ�����ڵ���ʱ������ȷ���ӳ�ʱ��ȡ�����ж��¼��ķ���ʱ����

��������������ֻ��1���жϴ����뵽�õ�CPU����Ӧ���ӳ�ʱ�䡣���������CPU��Ӧ1���жϵ����жϵõ���Ч�������ӳ�ʱ�䡣���ھ����жϹ��ܵ�PICϵ�е�Ƭ�����͵���ƷPIC16C5X��PIC12C5Xϵ�в��߱��жϹ��ܣ������õ��ǡ���Դ�жϡ�����Ʒ�������1���ж�������Ӧ�Ŷ���ж�Դ����ֻ��Ωһ��1���ж�����������˵ֻ��1���жϷ��������ڵ�ַ�������ζ�ţ����Ƭ�����жϷ������ֻ�ܱ�д1�������Ƭ����Ӳ���ṹ�õ��˼���ô����Ӧ����������Ͼ͵ö��һЩ����1���жϷ�������У�����Զ���ж�Դ�����������ͱ����ڽ����жϷ�����������ִ�е�������ж�Դ��һ�������ָ������ܶԲ鵽���ж�Դ����������Եķ���������������γ���1���жϴ�CPU��Ӧ����������Դ������ӳ�ʱ�䡣��ʱ���г��ж̣��������ű����ŵ��ж�Դ�ĸ��������Ӷ����ӡ���������ֻ��1���ж�Դ�����ţ���ʱ����Ҫ����ж�Դ�Ϳ���������������Դ����������������ж�Դȫ�����ţ���ʱ���ڼ���ж�Դ�ϵ�ʱ������

���Ĺؼ��֣���Ƭ�� Ƕ��ʽϵͳ-��������Ƭ��-�����豸 - Ƕ��ʽϵͳ-����

��һƪ����Ƭ��ϵͳ�ĵ�����ƵIJ���