点击看原图

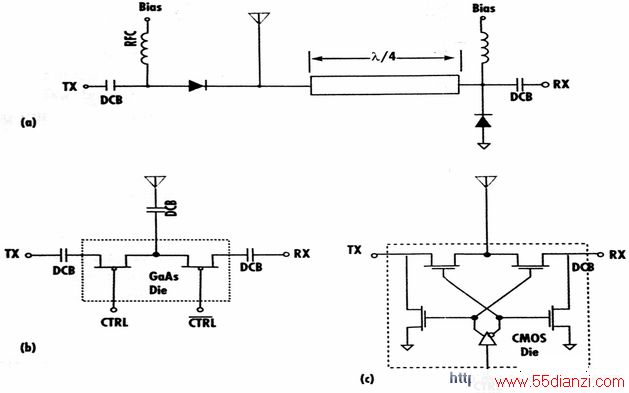

&nb sp; 图1、SP2T开关结构:(a)PIN二极管; (b)GaAs IC; (c)RF CMOS IC

上世纪七十年代,PIN二极管的出现标志固体开关行业的诞生。PIN二极管具有极低的插入损耗和谐波器畸变,仍然是ASM的主导技术。然而,PIN二极管存在着自身的缺陷,不能构成完整的ASM。为了偏置二极管,模块需设置隔直电容和供电电感。为了制作多刀开关,又需用四分之一波长的二极管串、并联组合(见图1a)LTCC中,900MHz的四分之一波长相当于几个厘米,这些传输线增加了二极管基ASM的尺寸。

GAAS PHEMT(准晶高电子迁移率晶体管)开关(见图1b)能减少ASM的体积并降低其复杂度,已成为除PIN二极管外又一种可行的替代品。采用GAAS开关,每条路径需用多个FET,还需一条控制线。此外,与PIN不同,PHEMT FET本质上承受不了17.8Vpk GSM信号。只有将多个FET串联在一起,将电压分散到每个器件,才能满足功率容量要求。并联FET能提高隔离度,增强抗扰度,当然控制信号数也要从6个翻番至12个。为了满足GSM的35dB隔离度要求,必须使用并联FET或级联开关。

为了减少PHEMT ASM接口的复杂性,通常在ASM中备有一个CMOS 译码芯片。尽管能实现增强型和耗尽型两种器件的PHEMT工艺已在研发之中,但目前仍不能在PHEMT中制作互补器件,因此无法实现静态逻辑器件。附加CMOS芯片会增加面积和路由的复杂性。要想防止RF耦合至控制信号,布局设计时要谨慎行事。

GAAS开关的ESD承受能力较低,通常为250~500V,需另加保护。正是这一要求与实现困难度两方面因素,迫使很多设计人员放弃真正的SP6T开关,转而改用2个SP3T和双工器组合结构。双工器提供ESD保护,代价是设计中增加了0.4dB插入损耗。某些供应商选择另一种实施方案,即在单个IC中将SP4T和SP3T级联起来。SP4T的输出路由至RX端口,形成RX与TX两个开关的串联。这个方案在频带重叠区提供适当的隔离来保护LNA,但同时也增加了插入损耗,从而增加噪声值。

GAAS开关是用耗尽型FET制作的,其负VGS值应低于截断电压,将器件关闭。此外,要想和来自CMOS逻辑的正控制信号一起工作,FET是隔直的,且源和漏要偏置在CMOS电源VDD电压。这样才有可能用O_VDD信号来控制GAAS开关。隔直电容可集成在LTCC中,虽然它会增加面积和LTCC衬底的层数。

最近,RFCMOS异军突起,并已进入前端开关领域(见图1c)。传统上,RF CMOS仅适合低压应用,但器件和电路技术的突破,使RF CMOS开关完全能满足GSM的各项要求。

www.55dianzi.com

Ultra CMOS 技术

RF CMOS工艺可分为两大类:体硅工艺和SOI(绝缘体上硅)工艺。由于体硅CMOS在源和漏至衬底间存在二极管效应,造成种种弊端,多数专家认为采用这种工艺不可能制作高功率高线性度 开关 。与体硅不同,采用SOI工艺制作的RF开关,可将多个FET串联来对付高电压,就象GAAS开关一样。

SOI的一个特殊子集是蓝宝石上硅工艺,在该行业中通常称为Ultra CMOS。蓝宝石本质上是一种理想的绝缘体,衬底下的寄生电容的插入损耗高、隔离度低。Ultra CMOS能制作很大的RF FET,对厚度为150~225μm的正常衬底,几乎不存在寄生电容。

Ultra CMOS 工艺的基本结构如图2所示。晶体管采用介质隔离来提高抗闩锁能力和隔离度。为了达到完全的耗尽工作,硅层极薄至1000A。硅层如此之薄,以致消除了器件的体端,使它成为真正的三端器件。目前,Ultra CMOS 是在 标准6寸工艺设备上生产的,8寸生产线亦已试制成功。示范成品率可与其它CMOS工艺相媲美。

上一篇:USB接口类单片机特点及应用