为了有效地节省语音数据的传输带宽和存储系统的磁盘空间,需要在保证语音质量的前提下尽可能降低其编码比特率。本设计采用经过优化的G.729语音压缩编译码算法,以ARM处理器为载体,开发的嵌入式语音存储系统可实现语音信号的海量存储,而且处理速度快、可靠性好、扩展方便。通过严格的测试和评估,该系统能够实现对大量语音数据的压缩和记录,各项指标基本达到了预期的水平。

1 系统控制核心

嵌入式操作系统软硬件结构框图如图1所示,由硬件层、驱动层、系统层和应用层组成。硬件层包括嵌入式处理器最小系统、存储器(SD RAM、Flash、ROM等)、通用设备接口和I/O接口(A/D、D/A、I/O等),其中Linux实时操作系统和应用程序都可以固化在ROM中。硬件层的核心是嵌入式处理器,在一片嵌入式处理器基础上添加电源电路、时钟电路和存储器电路,就构成了一个嵌入式处理器最小系统。中间的驱动层将上层软件和底层硬件分离开,为其连接提供接口。系统层主要负责软件硬资源的分配、内存管理、任务调度、文件处理等,是软件层的核心。应用层为用户提供编程接口,实现各种应用功能。

1.1 系统软件核心

Linux操作系统的内核主要由进程调度、内存管理、虚拟文件系统、网络接口、进程间通信五个子系统组成,各个子系统之间都存在着不可分割的依赖关系。内核为设备驱动提供支持,实现设备控制与应用;设备驱动为上层提供标准接口,完成硬件细节的封装。可以根据设计需要对内核模块进行适当的裁减,制作出理想、实用的操作系统。

1.2 系统硬件核心

Samsung公司的S3C2440A处理器是一款以手持设备为主而设汁的芯片。这款处理器支持NOR Flash和NAND Flash启动方式,内部集成LCD、I2C总线、AC97、Camera等控制器。提供丰富的接口资源,方便与外设连接,易于扩展。

2 G.729算法概述

2.1 G.729编码原理

G.729编码标准采用CS-ACELP语音压缩编码技术,其核心原理是线性预测和二级量化。每个10 ms的语音帧包含80个采样点,在每个这样的语音中都要进行线性预测(LP)分析,计算出LP滤波器系数,再转换为线性谱对参数(Line SpeCTRum Pari,LSP),并使用有两个阶段

的预测矢量量化器(Vector Quantization,VQ)进行18比特量化。然后编码器以原始语音和合成语音的误差感觉加权最小为准则采用A-B-S(Analysis-By-Synthesis,分析合成)方法搜索激励信号,激励参数(固定码书参数和自适应码书参数)每个子帧(5 ms帧长,40个采样点)确定一次,感觉加权滤波器的系数由未量化的LP系数产生。

2.2 G.729解码原理

解码是编码的逆过程,其原理为:首先从获得的码流中提取出参数的索引,这些参数包括LP滤波器系数、自适应码书矢量以及固定码书矢量和增益,它们分别解码后,可获得一个LSP系数、两个音节延迟、两组自适应码书和固定码书增益等对应于10 ms语音帧的编码器参数。

然后将LSP系数进行内插操作,转换为每个5 ms子帧的LP滤波器系数,再对每个子帧进行如下操作:

①经各自增益缩放的自适应矢量和固定码本矢量相加,得到重建的激励信号;

②将激励信号通过LPC合成滤波器,得到重建语音;

③重建的语音信号经过各种滤波器的后续处理,实现信号的放大和改善。

2.3 G.729算法优化

在G.729编码算法中,采用量化码本结构。其基本原则如下:首先计算出K维码本里的各个码字矢量的平均值并存储起来;然后求出输入信号矢量平均值和各个码字矢量平均值的均方误差值;最后用遍历法找到这些均方误差中的最小值Dmin,与之相对应的码字即为最佳逼近码字。采用这种搜索方法加快了编码速度,减少了搜索时间,并没有改变矢量量化的精度。

3 系统硬件结构

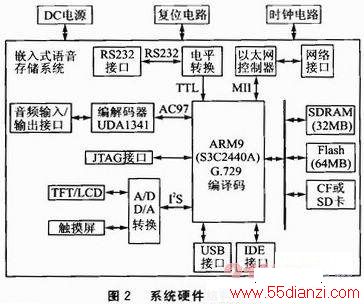

系统硬件结构框图如图2所示。S3C2440A作为整个系统的主控芯片,DC电源、复位电路、时钟电路作用于系统的每个部分;存储模块包括SDRAM、Flash以及外接的CF或SD卡等;调试模块包括JTAG接口、RS232接口以及网络接口三个部分;音频模块的主要工作由编解码器UDA1 341完成,扩展接口由USB接口、IDE接口构成,交互模块由TFT LCD和触摸屏构成。其中,音频模块和IDE扩展接口是研究的重点。

3.1 系统外围电路

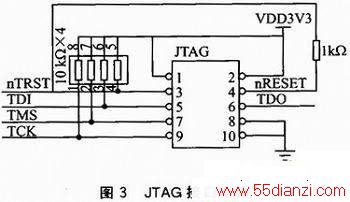

系统设计的外围电路都是ARM最小系统所必需的。电源电路为系统提供能量,是系统工作的基础。设计电源电路时要考虑的因素很多,主要包括输入及输出的电压范围、输出纹波大小、电池兼容和电磁干扰等,系统采用DC-DC转换芯片LM1117将5 V的电压转换成1.3 V、2.5 V、3.3 V后供系统使用。采用复位芯片MAX811产生的复位信号,既能保证上电复位的时间,又能保留手动复位的特点。时钟电路为系统提供工作时钟,主时钟采用12 MHz晶振作为时钟源,RTC时钟采用32.768 kHz晶振作为时钟源。通过JTAG接口,可以访问芯片内部的所有部件,是实现系统开发、调试的高效手段。为了减小系统体积,采用10针简化的JTAG接口,其接口电路如图3所示。

SDRAM存储器选择Samsung公司的K4S561632E-UC75,其存储容量为32 MB,具有存取速度快、成本低廉的特点,主要用来存放执行代码和变量,是系统启动之后主要进行存取操作的存储器。Flash存储器选择Samsung公司的K9F1208U0CNAND Flash存储器,其存储容量为64 MB,可以擦写一百多万次,具有很长的使用寿命,把启动程序、内核代码等固化到Flash闪存中能加速系统的启动、提高系统的稳定性和可靠性。

3.2 音频采集与处理模块

该模块采用Philips公司生产的音频芯片UDA1341TS,它支持I2S数据总线格式,且具有低功耗、低电压及DSP语音功能等特征。I2S(Inte grate Interfaceof sound)是Philips公司提出的串行数字音频总线协议,音频数据与控制信号、时钟信号分开传输,避免了由时钟带来的抖动问题,因此系统中可省略消除抖动的器件。

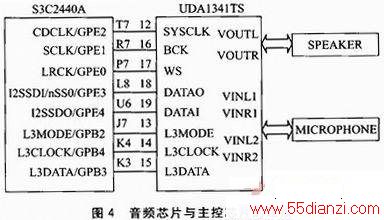

音频芯片与主控芯片的连接如图4所示。I2S音频接口包括5根信号线,其中音频模块的同步时钟CDCLK由S3C2440A提供,该时钟控制音频的A/D、D/A采样速率。串行时钟SCLK,也叫位时钟(BCLK),即每一个SCLK脉冲对应一位数字音频数据。帧时钟LRCK用于左有声道的切换,LRCK为1表示正在传输的是左声道的数据,为0则表示正在传输的是右声道的数据。DATAI是串行数据输入信号线,DATAO是串行数据输出信号线,所传输的音频数据用二进制补码表示。L3总线接口包括3根信号线:L3MODE/GPB2是微处理器接口模式信号线;L3CLOCK/GPB4是微处理器接口时钟信号线;L3DATA/GPB3是微处理器接口数据线。L3总线接口主要用于传输控制信号,相当于混音器控制接口,可以调节输入/输出音频信号的音量、低音提升、控制去加重等。

3.3 IDE硬盘控制模块

IDE接口是硬盘和光驱普遍使用的外部接口,接口采用16位数据总线并行传送,体积小、速度快,兼容性强。IDE接口主要有可编程输入输出(Programming Input Output,PIO)和直接内存访问(Direct MCMory ACCess,DMA)两种传输模式。PIO模式占用大量的系统资源,数据传输速率较低;DMA模式需要额外的驱动程序或设置,系统资源占用少、执行效率较高。本设计选择DMA模式。

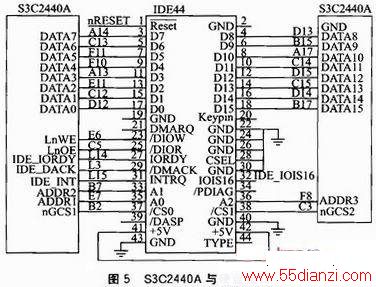

S3C2440A与硬盘接口如图5所示。其接口信号分为片选信号、数据信号和控制信号3个部分。硬盘上寄存器分为两组,分别由/CS0和/ CS1选中其中的一组,A0~A2引脚用于组内寄存器寻址,包括数据寄存器、错误寄存器、扇区计数器、扇区号寄存器、低柱面号寄存器、高柱面寄存器、状态寄存器和命令寄存器。数据线D0~D15用于数据的双向传输。/DIOR、/DIOW是读写控制信号;/Reset是硬盘复位信号;DMARQ(DMA请求信号)和/DMACK(DMA应答信号)是专用于DMA模式的信号。

4 系统软件实现

4.1 语音数据的采集

语音采集部分主要是完成UDA1341TS驱动程序的编写,其初始化相关代码如下: