Ƕ��ʽϵͳ�����Ĺ�����������ռ��Ƕ��ʽ����ר����������һ�����ϡ��˽�Ӳ����������Լ��������ܽ�������⣬��ѡ����ȷ�ľ�Ƭ����������ϵͳ�Լ��������Ч�ʵĹؼ���

�ܶ��˶�����"����(bug)"��һ�ô���Դ�ں����ٽ� Grace Murray Hopper������ʵ�ϣ�û��֪�������÷���������Դ�������ܿ��Ի��ݵ� Thomas A Edison�����������硣�����������۾��� Hopper �� 1945 �� 9 �� 9 ���ڹ����ѧ�� Mark II Aiken �̵������( Relay Calculator)���в���ʱ���ڶ�·�� Panel F #70 �ż̵�����������һ˫���档������ֻ�����õ���(���ǶԵ��Խ��г�����(debugging))���ͽ������̨��������ʱ�ػ��Ĺ���(�ο����� 1)����Ȼ������ڵ�����ָ���Ǵ�ϵͳӲ����ȥ�����棬������"debugging"�������ָ����һ����ʽ�����⣬��ȥ��ȱ�ݴ���(defective code)�Ĺ��̡���Щ��������κ���ԭʼ����IJ��죬��ȥ��ȱ�ݴ����������Զ�������Ӿ�������(correction code)����������£����κ�ʱ�䶼���Ի�����е�����(��ϵͳ�ąR�������ݴ���ֵ)����������ġ������� IC ת�� SoC���ɴ�ȡ��(aCCessibility)�ͱ�ø��������ˡ�

��Ӳ���������Ҫ�����ܵؿ��Դ�ȡ��Ƕ��ʽϵͳ�ڲ���Դ����������۲�ϵͳ�����ԣ��� CPU ״̬�� PC ֵ������ϵͳ�IJ�������Ƕ��ʽϵͳ��Ƶ����ڿ����ü������г��������¼(logging)���أ����߶Զ���� SoC���ԣ����Բ������¿����ķ���������١�������������(cache debugging)�ͽ��津��(cross-triggering)�ȡ����ĵ��ص㲻������α�д�����Ϊ��������������������ڿ��õ�Ƕ��ʽӲ����Dz�Ȩ(intellectual property ��IP)���Լ��� IP �ܽ���ķ���ij������⡣

��¼����

�����Ҳ����õij������������ڴ���������һЩ��ӡ����(print statement)����������ʾ����ij�����ֵ�ִ����Ѷ�����ṩ�ݴ����ͱ�����ʵ��ֵ���������һ�꼶ѧ����ϰ"hello world"��һ���������ó�ʽ����ӫĻ����ʾ�������ʣ����ڱ�ʾ��ʽ�ܹ����У��Լ�ִ�е���ij���㡣��ӡ����(�� printf ���)ֻ�Ǽ�¼��һ�ֱ��ͣ������ô���������Ҫ��Ѷд��һ��"�ܵ�(pipe)"����Ϊ�ⲿ���ٵĹ��̡���ʹ�õĹܵ�����ϵͳ�������� printf ����£��ܵ��DZ������(ӫĻ)������Ҳ������ UART��USB��������ͨ�� I/O��

������Ҫ��һ�ֶԳ�ʽ��ƹ���ʦ������ķ�ʽ����֯����������Ѷʱ(�����ṩ�в�����Ѷ��״̬����ת��)�����ü�¼�ķ����Ǻ��м�ֵ�ġ������ü�¼������������¼����Ѷ��������һ���������Ͽ⡣����С��ʹ�ü�¼���ܲ��ܻ�ø�Ч�ʡ����磬��¼��ѶӦʹ�ùؼ��ֿ�ͷ����"����"��"����"��"����"�ȣ���Ӧ��ʶ�����Ѷ�Ľ����ߡ�Ӧ����¼���ܻ���ΪһС�鵵�����Ա���ά�������ṩʱ�����Ѷ�����ҵ��ǣ���¼��һ�������Եķ���������������ļ�ʱ״̬�������ͬ������Ӧ�á�

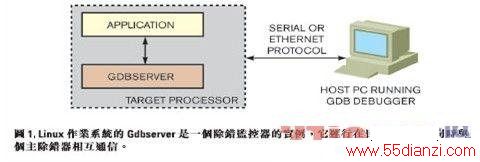

�������������һ�ֳ����ij������ߣ����������� CPU �������е�Ŀ�����һ����(�ο����� 2 �Ͳο����� 3)��������������һ̨�����ϣ�����һ��ר�õIJ�����ָ��ͽ�����Ӧ���Ӷ��ﵽ������ͨ�ŵ�Ŀ�ġ����Խ� Linux �ϵ� gdbserver ��ʽ����һ������������������������ڵ� ROM �����������

(ͼ 1)��

��ʹ����ϣ����ij��ָ�����һ���жϵ�ʱ��gdbserver �ᱣ���ָ�����һ��ϵͳ����(system call)���������Gdbserver Ȼ���� Linux �� ptrace ��ʽ������н���ϵͳ���е�Ӧ�ó�ʽ��Ѷ�����ţ�������ϵͳ���ж������жϵ�ʱ��gdbserver ����ȡ�öԱ�����Ӧ�õĿ��ơ�������������һ̨���ػ��ϣ������в�����̫��·���ӵ�Ŀ�����(�ο����� 4)��������ķ����ȱ�����ʵ�ã���Ҳ��һЩȱ�㣬������Ҫ�ڽ����κγ���ǰ������룬��������Ӧ�������Ӱ�졣�������λ�ڿ����������оͲ���ʹ�ü�������壬��ΪҪ���������жϵ����Ҫ��Ӧ�����塣

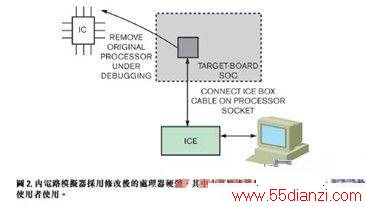

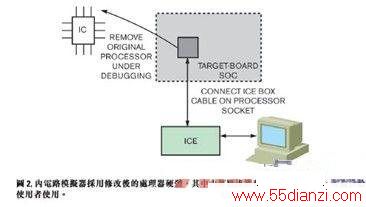

�ڵ�·ģ��

�ڵ�·ģ����(in-circuit emulator ��ICE)�ǵ�һ����Ӳ��Ϊ�����ij���������������������������һ���汾��ICE ͨ��ʹ��һ���ֳ��ɱ��բ����(fiELD-programmable gate array��FPGA)��FPGA ���(bond out)���ڲ��R���ź�״̬�źţ�����ʹ���߿���ʹ������(ͼ 2)��

ICE �ṩ�ij������ܶ��� ROM �������ʹ�� ICE ʱ��������һ�����ӵ� ICE �е������滻��������·���ϵĴ�������һ�����в�ģ����������ܵ������������ ICE �С�ICE ����Ҫ������֮һ�����ļ۸����⣬��Ȼ����������ʺϼĴ����������ִ� SoC �и��ߵĸ����ԡ����϶Ⱥ�Ƶ�ʣ���� IC ��Ӧ������Ϊ�ִ��������ṩ ICE �汾��

һЩŷ��˾��1985 ����������ϲ��Ի��(Joint Test Action Group��JTAG)��������˳���Ҫ������뵼�� IC �ĸ������⡣����Ϊ IC �ı߽�ɨ����Խ����� IEEE 1149.1 �������� 1990 �깫���˴�һ��(�ο����� 5 �� ͼ 3)��

JTAG ��������һ������ I/O JTAG �����ж������źţ�������ͨ����ɵ�·�IJ��������������ʱ�(test cLOCk��TCK)������ģʽѡ��(test-mode select��TMS)����ѡ�IJ����ض�(test reset�� TRST)���������ϵ�¼(test-data in ��TDI)�� �����������(test-data out��TDO)��

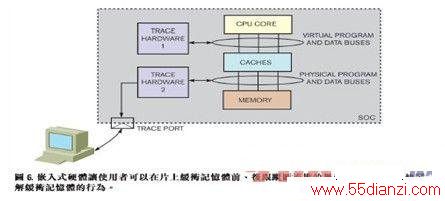

IEEE �� JTAG Ӳ�彨����һ�� 16 ̬������״̬(finite-state)���ϣ����� TMS �źſ��ơ�TCK��������ʱ�(rising- edge clock)�Xȡ����һ TMS �źš�������Ѷ��TDI ��(TDI pad)���룬����TDO ���Ƴ�������� TRST ������������趨��IC ��ÿ���涼��������ɨ���ݴ��������������ڲ�������������һ���߽�ɨ������������ TDI/TDO �� JTAG �������������Ƴ����Բ��Ե�·���ϵ��ⲿ���ӣ����� IC �ڲ��������ӣ��Xȡ IC ���ֵ������ JTAG ������·ģʽ��JTAG �ṩ�˵ͳɱ����u����Թ��ܣ�����Ϊ��õIJ��Է��������ǣ�������������ʹ�á��߿����Ժ͵ͳɱ�ʵ�ֵ��ص㣬����߾������ JTAG �������������Դ�ȡƬ�ϵij�����Դ(�ο����� 6)��

JTAG �dz���ͨ�ŵĴ���㣬λ�������������ϵij�������Ƕ��ʽ������������Դ֮�䡣������������ݴ������Դ�ȡ�����е�Ӳ�� IP������ ICE �����˳ɱ����ܶ�뵼�幩Ӧ�̽��������Ӳ�������ھ�Ƭ�ϣ��Խ���������Ƶ����⣬���ṩ�� ICE ���ƵĹ��ܡ�Ƭ�ϳ���Ӳ���һ�ֳ���ʵ���Ƿ�˼�����뵼�幫˾�� 68-kbit Coldfire Ƕ��ʽ�������� PowerPC(������ Power �ܹ�)�������ϵı�������ģʽ(background debugger mode ��BDM)��������Ӧ��Ҳ�����ƹ��ܵ�ר�����ơ�

Ƭ�ϳ���Ӳ��������һЩ���ܣ���Ӳ���жϵ㡢�ڲ��ݴ�����ȡ����/д�������壬�Լ��۲��(watchpoint)�ȣ���Щ������ǰֻ���� ICE ʹ�á���һ���ദ���� SoC �У����Խ�ÿ�龧Ƭ����Ӳ�����ӵ��� JTAG ����������ͬ��Ӧ�̵����ӿ���������ͬ�������͵���������Ƭ�ϳ��� JTAG ״̬������������֮�佨����һ�� TDI-TDO JTAG ��(ͼ 4)��

����

��ʱϵͳ��������������֮һ���Ǻ�ɭ���ij���(Heisenberg bug)����̽��ЧӦ(probe effect)��Ϊ�������ض����ӵ��κ������Ӳ�嶼���ܸı伴ʱϵͳ����Ϊ����������������������������Ѷ������ʱ���ͻᷢ�����������ʹ�ó���Ӳ��ʱҲ�������Ƶ�Ӱ�졣���磬Ƭ�ϳ���Ӳ����ܽ���������ִ�������ĵ������жϵ㴦����������������Ӳ�����"͵ȡ(steal)"�Ӵ�������������IJ���Ƶ�����Ա�����������������Ѷ��

����Ӳ�廹������ UART ��������¼��Ѷ������Ʒ����Ҳ����ʹ��������档ICE ͨ���ṩ������ʽ�ĸ��ٹ��ܣ������߿������κ�ʱ���ȡ�������ij�ʽ��������Խ��Խ��� SoC ��Ӧ�����ڰѸ���Ӳ�����ϵ���Ƭ�ϣ����ṩ���ƵĹ���(ͼ 5)��

��ר�õĸ���Ӳ�塢ר�õĸ��ٲ������������봦�������Ϸ�������υR���ţ��Լ� JTAG ���棬ʹ����Ӳ�����ʵ�ַ�����ʽ�ĸ��١�

���Ĺؼ��֣�Ƕ��ʽ Ƕ��ʽϵͳ-��������Ƭ��-�����豸 - Ƕ��ʽϵͳ-����