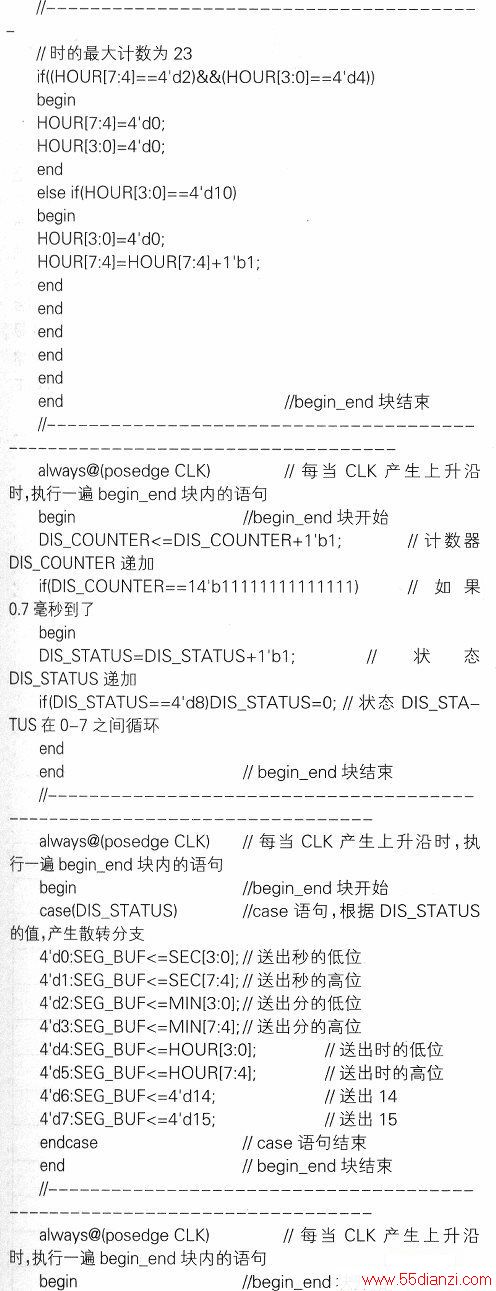

9.RS232收发不同内容的实验

1、实验要求在PC机上使用串口调试软件发送一个字节,MCU&CPLDDEMO试验板收到后驱动发光二极管进行相应的指示,同时读取按键开关的状态并发回PC机。

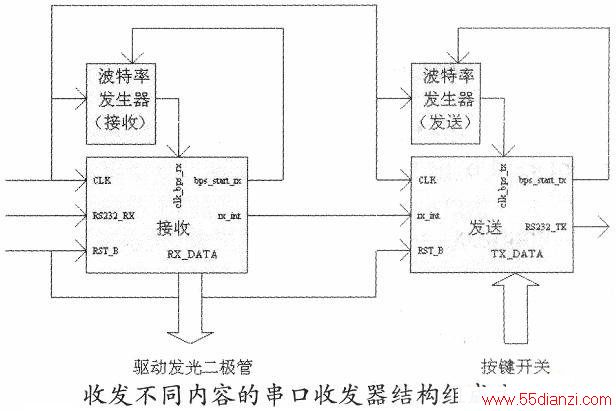

2、实现方法串口收发器收发不同内容的结构组成方框图见上图。我们以波特率9600、数据位8位、停止位1位为例进行设计。因为MCU&CPLDDEMO试验板上的有源晶振频率为24MHz,所以波特率9600的分频数是24000000÷9600=2500,波特率9600的分频数一半是24000000÷9600÷2=1250。

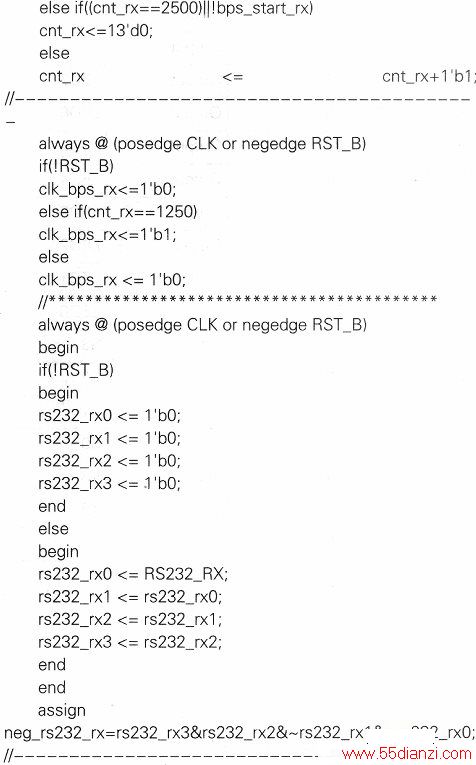

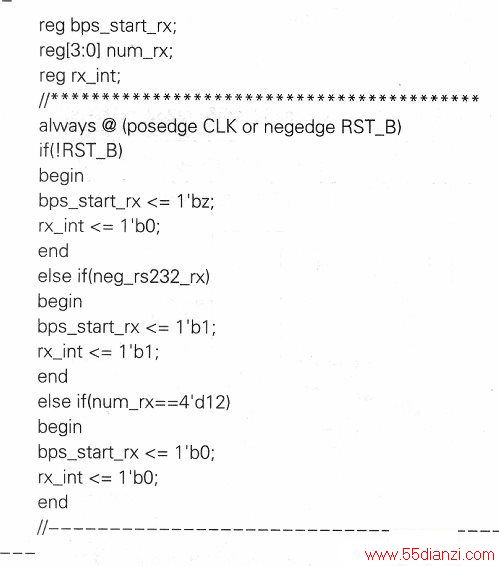

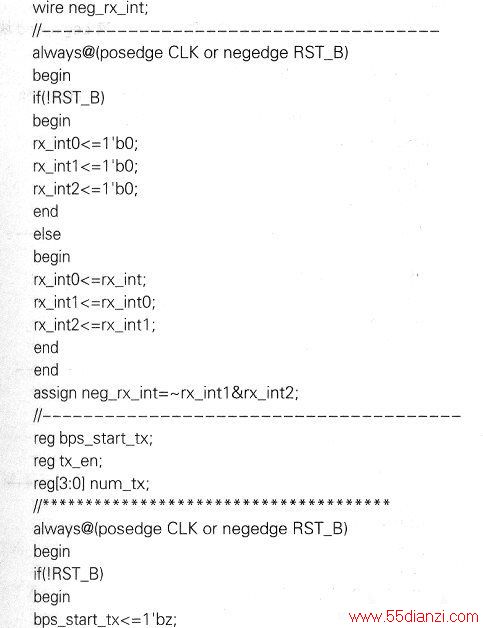

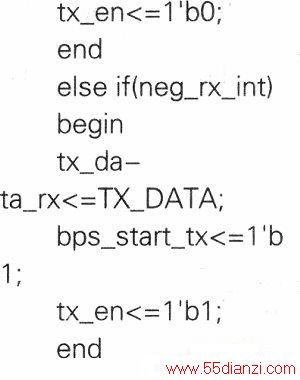

平时,RS232_R×为高电平。当串口接收电路检测到输入端RS232_RX出现下降沿时,将bps_start_rx置高,启动接收波特率发生器,产生波特率时钟脉冲clk_bps_rx,同时开始从RS_232R×端接收串行数据,并且同步启动接收移位次数计数器工作,每个接收波特率时钟的高电平接收一位数据。在标准的接收模式下,有1+8+1(2或3)=12位的有效数据。收到停止位后,接收移位次数计数器清零,并将数据锁存到输出寄存器中,驱动发光管指示。

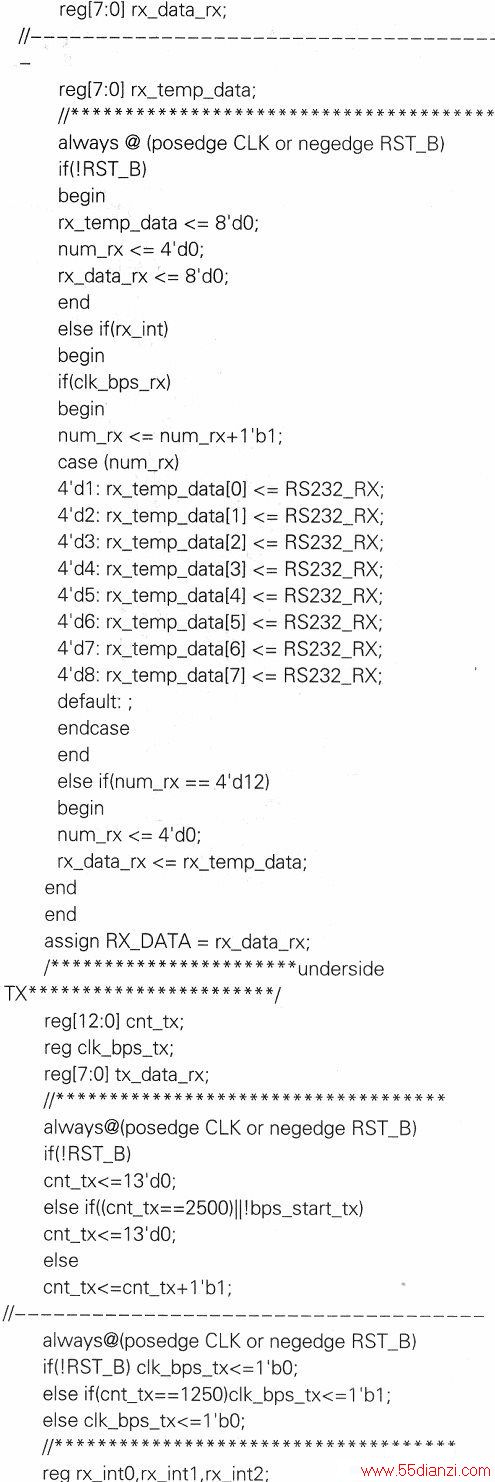

在串口接收电路收到数据期间时,将接收数据中断信号rx_int置高,根据此信号启动发送波特率发生器,产生波特率时钟脉冲clk_bps_tx,同时电路读取按键开关的状态,从RS232_TX端将按键开关的状态数据发送回去,并且同步启动发送移位次数计数器工作。每个发送波特率时钟的高电平发送一位数据。在标准的发送模式下,有1+8+1(2)=11位的有效数据。发送结束后,发送移位次数计数器清零。

3、程序设计在D盘中先建立一个文件名为RS232_RXTX的文件夹,然后建立一个RS232_RXTX的新项目,输入以下的源代码并保存为RS232_RXTX.v。前面我们已经对串口的通信程序作了详细的分析,因此下面的这段程序就不作具体分析了,留给读者自己研究。

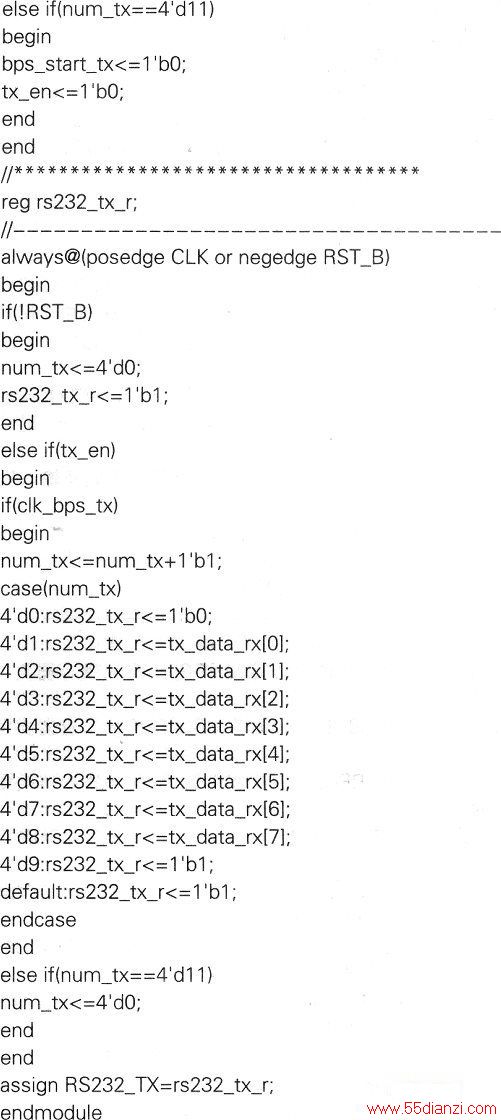

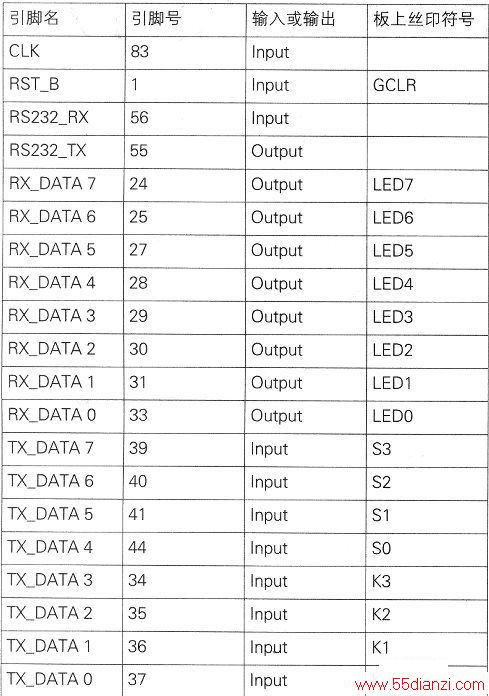

源代码输入完成后,我们将器件选择为EPM7128SLC84-15。引脚分配需要参考MCU&CPLDDEMO试验板的电路原理,这里的引脚分配见下表。

器件编译通过后,可根据需要进行仿真,接下来进行*.pof至*.jed的文件转换,最后将*.jed文件下载到ATF1508AS芯片中。CLK,RST_B,RS232_RX,R×DATA,RS232_TX,TX_DATA

取一条串口线,一端插在MCU&CPLDDEMO试验板上CPLD_DB9插座上,另一端插到PC机的串口上。为了防止传输混乱而收不到数据,首先将MCU&CPLDDEMO试验板通电,按动一下GCLR键,将发送缓冲区的乱码清除。然后在PC机上,打开串口调试器软件,清空发送、接收区内的数据,发送、接收均选择“按16进制显示”,然后点击“打开串口”按钮。发送区输入F8,同时按下MCU&CPLDDEMO试验板上的K3-KO按键,点击“发送”,我们看到我们看到试验板上LED2-LEDO立刻点亮(下图),同时接收区也显示出了按键开关的状态“FO”(下图),实验 获得圆满成功。

10.简易数字电子钟

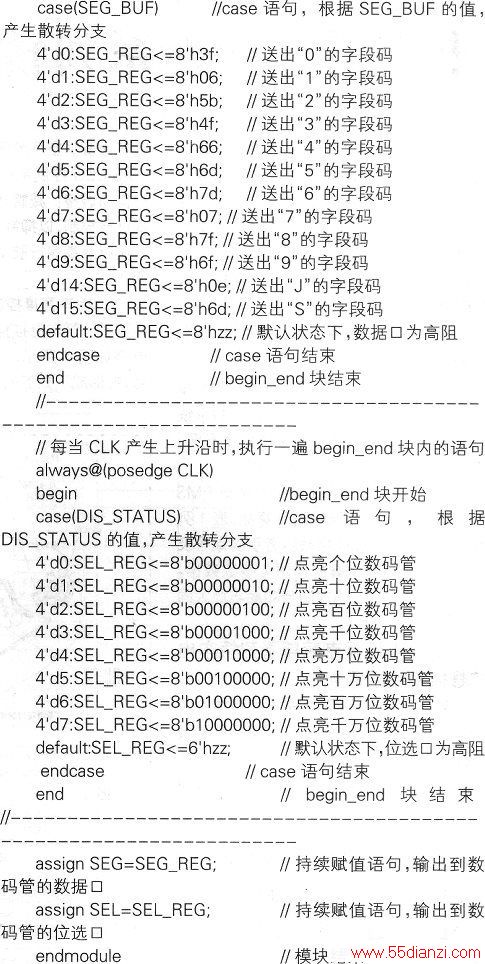

1、实验要求设计一个简易数字电子钟,显示的时间范围为:SJOOOOOO~SJ235959,可以循环计时。说明:SJ代表时间的汉语拼音,000000代表00时00分00秒,235959代表23时59分59秒。时间过23时59分59秒后,又从00时00分00秒开始计时,反复循环。

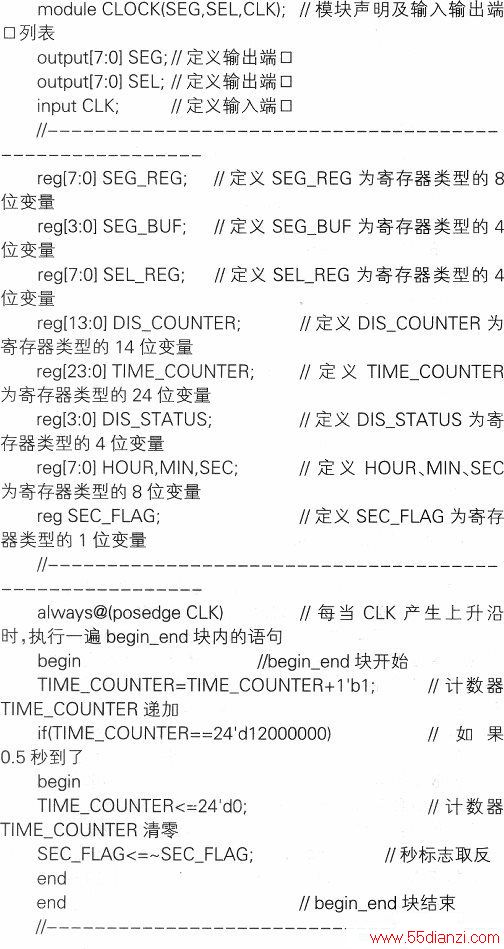

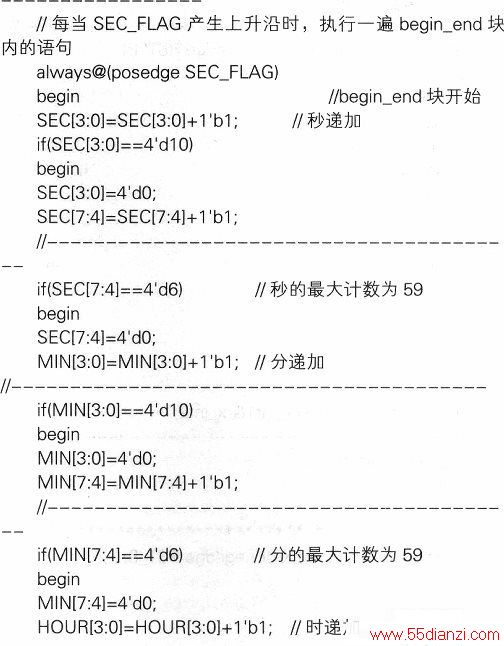

2、实现方法设定一个时间计数器,每隔0.5秒产生一个秒标志(即每秒产生一个脉冲),然后分别用秒、分、时计数器计时。计时时必须遵循时间规律,即秒、分按60进制,时按24进制。另外还要设定一个数码管显示用的扫描计数器,每隔一定时间(例如0.7毫秒)点亮一位数码管,循环扫描点亮。这样由于扫描的时间很快,8位数码管的扫描周期还不到6毫秒,远低于人眼视觉暂留特性的限定值,故可以看到稳定的显示。

3、程序设计在D盘中先建立一个文件名为CLOCK的文件夹,然后建立一个CLOCK的新项目,输入以下的源代码并保存为CLOCK.v。

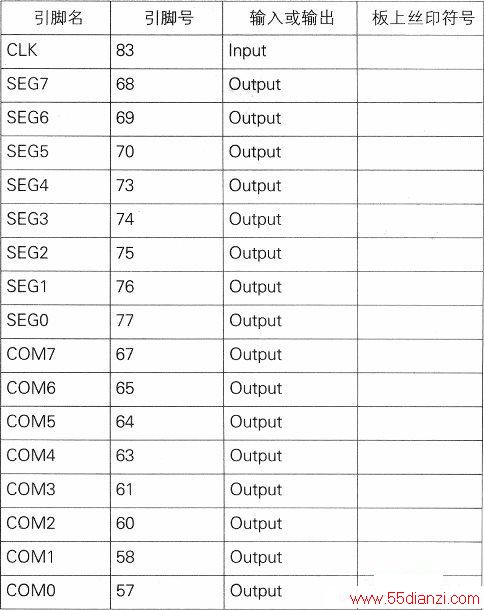

简易数字电子钟的引脚分配

源代码输入完成后,我们将器件选择为EPM7128SLC84-15。引脚分配需要参考MCU&CPLDDEMO试验板的电路原理,这里的引脚分配见表12。器件编译通过后,可根据需要进行仿真,接下来进行*.pof至*.jed的文件转换,最后将*.jed文件下载到ATF1508AS芯片中。在MCU&CPLDDEMO试验板上,我们看到8个数码管从“SJOOOOOO”开始计时(见下图),计时非常准确。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术