基于实现更加精确无线信道模拟的目的,采用了数字信号处理的方法实现对空中无线信道的模拟。在本文中,首先介绍无线信道的多径信道模型,主要包括衰减、时延以及多普勒频偏等无线信道的基本要素;随后给出了实现多径信道模型的设计和实现思路,给相关人员提供一定的参考。

无线通信作为通信领域的重要组成部分,现在已经得到越来越广泛的应用。特别是随着数字信号处理技术的不断发展,以及智能移动终端概念的出现,无线通信与人们的日常生活越来越紧密;因此,各厂商都加大了对无线通信研发的投入,无线通信产品层出不穷。

由于无线通信自身的特点使得在无线通信设备研制过程中,需要在外场的实际通信环境中进行反复实验和验证,才能保证产品的性能和质量。众所周知,在外场实验中,需要投入大量的人力和物力,而且问题的解决和重现难度很大;因此,要保证研制周期,也是件很困难的事情。

为了克服外场实验所带来的不利因素,在无线通信设备的研制过程中,信道模拟器得到越来越广泛的应用。本文就是针对信道模拟器的研制而提出的一种基于数字信号处理的实现方法。通过数字信号处理这种方法,可以较为精确地模拟信号的衰减、时延和多普勒频移等无线信道特征,而且与目前常用的延时器方法,本文所提到的方法更能有效地节省处理器资源。

1 信道模型

与有线信道不同,无线信道除了直射波外,还会由于反射、散射和衍射等现象的存在,信号会沿着不同的路径和方向到达接收端,此时接收到的信号会产生时延扩展现象;另外当接收机处理于移动状态时,各条径的信号也会产生不同程度的多普勒频移,从而使信号产生频域弥散的现象。

因此,基于多径信道模型,并考虑到信道响应的时变性,无线移动信道的二维冲激响应函数可以表示为:

![]()

式(1)中,ak、τk、φk、fk分别为第k条径的衰落因子、时延、相位和多普勒频偏,L为路径数。

令输入信号(发射信号)为![]() ,fc为载波频率,则输出信号(接收信号)y(t)为输入信号与信道冲击响应的线性卷积,如式(2)所示:

,fc为载波频率,则输出信号(接收信号)y(t)为输入信号与信道冲击响应的线性卷积,如式(2)所示:

![]()

式(2)中,fc为输入信号的载波频率。

由此可以看出,无线信道中的各条径彼此之间相互独立,多径信道就是将各条路径的信号进行衰减、时延以及多普勒频移,再将各条路径信号进行叠加而成。

2 信道模拟器设计思路

一般在无线通信中,载波频率都很高,直接对该频点的信号进行数字处理,是无法实现的。因此,对输入信号首先进行下变频处理,得到基带信号,经过AD转换得到采样信号进行数字处理,来生产多径信号,接收再由DA转换生成模拟信号,最后经过上变频生成输出信号。

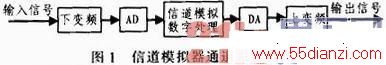

图1给出信道模拟器通道系统框图。

图1中,给出一个通道的信号处理过程。其中,下变频和上变频模拟信号的处理部分,采用一般的处理方法即可,文中不做阐述。

AD模数转换器的选择,要根据信道模拟器对信号带宽的设计要求而定,通过奈奎斯特(Nyquist)采样定理,即fs>2f,AD的采样率至少保证是信号带宽的两倍;同时还要根据系统的精度要求选择合适的位数。

由于模数转换器AD位数的限制,12位的情况下,衰减范围大约在60 dB左右。可采用在模拟端增加数控衰减器的方法来增加衰减范围。但是随之而来也增加了实现的复杂度。

3 信道模拟数字处理的设计

信道模拟主要是通过数字信号处理过程实现的,图2给出信道模拟数字处理部分的系统框图。

如图2所示,在信道模拟数字处理中,首先由插值滤波器对基带输入信号进行插值,由源数据队列进行暂存,同时信道模型运算单元将运算完成的信道参数(如衰减因子、延时、多普勒频偏等)存放到信道参数缓冲区;信道模拟运算单元获取输入信号、信道参数和WGN进行运算,再送入到降采样滤波器,最后输出基带信号。

另外,维护系统、信道配置系统和监控系统是后台用户接口,可对设备进行维护(如系统升级、校准补偿等)、信道配置、运行状态监测控制等,可根据实际情况和需求进行设计,这里不再进行阐述。插值滤波器和降采样滤波器资料比较多,这里也不再进行说明,但原则上是产生的系统时延越小越好。

下面分别对其他各部分进行说明。

源数据队列的主要功能是对插值后的基带数据进行缓冲,采用双口RAM实现。为了提高系统对时延的支持能力和分辨率,原则上队列容量越大越好。以5μs时延、1 ns分辨率和12位数模数为例:(5 000÷1)×2=10 000字节。可以看出,通过加大双口RAM的容量可以模拟更长的路径时延,而不需要占用处理器的资源。

信道模型运算单元对所配置的模型进行运算,生成衰减因子、时延和多普勒频偏等信道参数,放入信道参数缓冲区。由于信道模型运算量大,采用DSP高速处理器+FPGA进行主要运算单元,并对信道模型运行进行优化,视具体支持的信道模型而定。

信道参数缓冲区主要是存放计算生成的信道参数。该缓冲区分两块,采用乒乓机制,每块缓冲区空间大小根据数据处理速度进行计算。

信道模拟运算单元由一系列运行单元构成,其结构框图如图3所示。

图3中,每个运算单元负责计算一条路径的信道,运算单元的个数也就是所支持路径数,每个运算单元相互独立,且并行计算(减小系统时延),求和后得到输出结果。其中,每个运算单元根据时延参数从输入信号获取信号数据。另外,每个运算单元可以根据实际的路径数按需配置。

以上给出了信道模拟数字处理的总体设计思路,具体实现细节需要考虑的内容很多,如时钟同步系统、定点精度、算法优化等等。最好在做实现的设计之前,对系统方案进行仿真,作为实现设计的参考依据。

4 结论

数字信号处理方法实现方法灵活,特别是能够产生精确的时延,可以对多径信道模型进行模拟,给无线通信的研发人员带来极大的便利;采用数字信号处理的方法是无线信道模拟的发展方向,随着硬件技术的不断升级,可以模拟越来越复杂的信道模型。

相比通过延时器模拟多径的实现方法,文中所采用的方法器件要求更低的情况下可以模拟更长的时延和路径数。

但这种方法目前也会引入较大的系统时延,一般在2μs左右,在某些特定的应用场景下,会带来一些不便。

本文关键字:无线 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术