��������������̸���

�������ֻ�������������ֻ��һ�鹦���Թ�Ƭ����Ҫ�����Ա����ָ����룬�����ڳ�ʼ�������������衢������Ҫ���ܡ���������ӵȡ�������Ҫ�������Ա���衰���ݡ�֮����ܿ�ʼ���������ȿɱ���̺��ֳ��ر�̣�Ҳ�ܹ����ж�����¶��塣

������һ���棬 FPGA Ҳ��һ�鹦���Թ�Ƭ�������ܰ���һЩ����Ĺ�����ģ��(��洢��)����ͬ�������ڶ��塰���ݡ�����ܹ���������FPGA��I/O��ѡ��ʹ����������Դ��ҿɲ��в�����������������һ��������Ҫ�����Ա�������ǡ���������

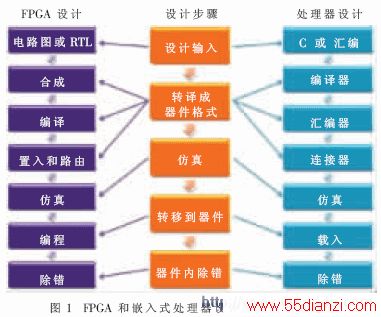

������ȻǶ��ʽ�����Ա����ͬʱ����FPGA��ƣ�FPGA�����Աһ��Ҳ����̤��Ƕ��ʽ�������ǵ����������ʵ��Ϊ���ơ���ͼ1��ʾ���������������ʱ���Ǵ��㿪ʼ������ij�����Ա�д����������룬Ȼ����������б�̺͵��ԡ����Ƕ��ܹ���Ƴ���ɫ�ֶ��ص�ʵ�ַ��������ܼ������һյ�ƣ�Ҳ���ܸ�����һ������Ʒ����Щ���ݼ��˱�д�����ݣ�ͬʱҲ��ζ���������ƫ���ڲ��л������Ҹ������ԡ�

��������Ƕ��ʽ��������FPGA

������ȥʮ�������������༯�ɴ�������FPGA�����д��������˵�FPGA�ʹ��д�����Ӳ�˵�FPGA�����Ǹ�������ȱ�㣬��������ЩFPGA�����Ҵ棬�е�ȴ������̭����������Ƕ��ʽ�� FPGA �����Ա��������̺��෴���Ծ����ڶ��̶����谭����Щ�����Ŀ��ٲ��ɡ�

���������������˵�FPGA

���������������˵�FPGA��Ҫ����FPGA��Ӧ���ṩ�IJ�Ʒ������������ΪFPGA�����Ա�ṩ�˳���Ƕ��ʽ��ƵĻ��ᣬ��������FPGA�����Ա��AVR��8051��PIC�� ARM �ȱ�������������ӵ���Լ��ĸ���ƫ�á�����ʹ���⣬�������������������Ƕ��ʽ�����Ա�������������ع�˾һֱ������Ϊ�����Ʒ�ṩ����������(��8051��Leon)��������Ƴ��˼�����ARM7��8051��ARM?�R Cortex TM-M1�������Ŀ���FPGA��

�������������˵�����һ�������(1)���Ը�����Ҫ�������裻(2)��ijЩ����ʹ�����й��ܵ�����£����Լ�ָ��Լ�Сռ�ÿռ䣻(3)����Ҫʱ���������ֲ�������FPGA�С�

�����������ַ����н����Ǵ�����������Ҫʹ���൱��Ĺ����������ɱ����ڶ���ʽ���������������������ӿ��ܵ���ʱ�����⣬���ⳬ����Ƕ��ʽ�����Ա�ľ��鷶Χ�����⣬SRAM FPGAû���������洢��������ݣ����Ա������ö������������������Ҳ��Ӱ�쵽I/OҪ��·���ͼ����Ƹ����ԡ�

��������ƽǶ�����������Ƕ��ʽ��Ƶ�FPGA�����Ա���ȱ�����FPGA�д�������Ӳ����ͼ���⣬Ȼ���ٽ���FPGA�ڲ�Ƕ��ʽӦ�õĵ��ԡ����ֻ��һ�������Ա���в�Ʒ���������������̻������Ǵ��л��ġ����������д���ȱ�ݻ����⣬����Ҫ�������������������ҳ�ԭ������(�Ǵ������⡢RTL���⣬����Ӳ��ʱ������)��������Щ��Ӱ���Ų�Ʒ������ʱ��Ϳɿ��ԣ����չ�ϵ���������ȫ����ɡ�

������Ƕ��ʽ������Ӳ�˵�FPGA

������������Ӳ�˵�FPGA�ж�����ʽ����Ϊ��ҵ����Ʒ����һ��ʮ�������ڼ��ٲ�Ʒ���ƹ�Ӧ�á����磬Triscend��˾ӵ��8051/ARM FPGA������÷��(Atmel)���Ƴ��˻���AVR��FPSLICTM����������Triscend��FPGA������FPGA������̷���ȱ����������Ը���������Ҫ��������һ�����Լ������Ĺ������̡�������������ܹ�����ֱ�۵����ϸ����������ȱ��һ��FPGA�û�������FPGA��ϸ��ƹ��ܡ�����÷��ӵ��FPGA���������������������FPGA/Ƕ��ʽ�������̣�����ͨ�����öԻ�����������Ľӿڡ�

������ЩFPGA������һ���ŵ㣬������ҵ����������������ŵ㻹���������ڲ���ҵ������������ܹ�ʹ��ҵ�����ȵı�����(��KeilTM��IAR SystEMS?�R)���Ӷ��ٴν�������Ƕ��ʽ��������Ӳ�˵���������ѱ�֤����˫����������������FPGA��������֮��ӿڵĵ��Կ�����һ����ս��

����һֱ�������ϸߵĹ�ɱ����Ǵ��д�����Ӳ�˵�FPGA��ȱ�㡣Ӳ�˴������ijɱ����dz��ӽ�����ʽ�������ijɱ�������ʱFPGA��Ȼʮ�ְ������˵����Щʹ��1��Ԫ��2��Ԫ������Ƕ��ʽ�����Ա�ڳɱ�ֻ��15��Ԫ���豸��ʹ��FPGA����Ҫ����һ����������裬��������Ա��ʦ��˵������һ�������⡣����FPGA�����Ա���ԣ���Щ�����е�FPGAʵ��̫С��������ܴ���Ȥ��FPSLIC����һ�������ĵ��ӣ�����ʦ��ϣ���ҵ��ⷽ�����Ŀ������һ�����붨�ۺ������Σ�������ᶼ������Ӧ�õ�ʵ������

����Ƕ��ʽ����������һ��

��������CMOS���յľ����ԣ�Ҳ��Ϊ���ڴ�Ӳ�˴������� FPGA ��SRAM FPGA�������û�м��ɴ�����ģ��ܡ������û��ڿ���������FPGA���п������ӹ㷺��ģ���·�����⣬ֻҪ������һ�����ڴ���洢�ļ���ʽ����ģ�飬������������������һ��������ģ���FPGA�ĵ�оƬǶ��ʽ�����������������������̽Ƕȿ��ǣ�����൱��������һ���µ�����������ʱ������Ҫ����FPGA��Ƕ��ʽ��ƣ����账��ģ����ơ����ǣ��������������������Ҫ����������ƣ�FPGA��ơ�Ƕ��ʽ��ƺ�ģ����ơ���Щ���������3����2������1�������Ա����ɣ�ʹ���������Ա�������ܹ����н����Լ�����Ʋ��֣��Ա�����������ӳ���FPGA�����˴�������Э�����⡣

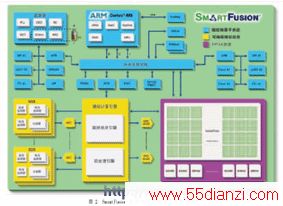

�������⣬����FPGA��Ƕ��ʽ�����Ա���dz�����û��Ŷӣ�������̱����˫��������������������û�ж��͵�ѧϰ���ߣ���FPGA��Ƕ��ʽ�����Ա�������ܹ�ȷ���Լ���רҵ���������ÿһ���������������������ѡ���ܹ�������Ҫ����ģ�����ݣ�ͼ2��ʾΪActel SmartFusionTM����ź�FPGA����ĿǰΨһһ�����FPGA�� ARM Cortex -M3������Ӳ�˺Ϳɱ��ģ���FPGA���������ļܹ����������Ĺ����Ա߽����ȷ����Ľӿڣ������ڼ�������������Ʊ߽硣

���������������ƹ������ֵĽǶ������з�����

����(1)Ƕ��ʽ�����Ա������ʹ�ó���������һ����ʹ�ô���һ�̶�Ӳ����(��ɫ����)�ı�ARM Cortex-M3������Ӳ�ˡ����Ϊ��������ϵͳ(MSS)�����ﲢ��ʱ��ȷ���ԡ���ģ���FPGA���κ����Ӷ�ͨ���Ƚ���������(APB)���Ƚ�����������(AHB)�ӿ���ɡ�����FPGA�����ݿ����кܴ�ı䣬�����ڴ洢��ӳ����м��Զ���չ�����ԣ����ĸ�������ɱ���Ϊ��������������չ���֡�

����(2)FPGA�����Ա����ѡ��ʹ��FPGA����ȫ�����ڴ������IJ��֡�����FPGA���й�����ȫ�����С�SRAM �� FIFOģ�飬�Լ����� LVDS ��I/O�����������Ա��������FPGA�ܹ������ơ���������FPGA�����ԱҲ�ܹ�ͨ�������Ƚ����������ܹ�(AMBA)������֧��Ƕ��ʽ��ƣ�������AMBA�ӿڿ����µĹ��ܣ��Դ������ר�õ��µĶ������衣

����(3)����ģ�����û�б����ֳ�������̣���ˡ�ģ����ơ��������Բ�ͬ�˵ĺ������Ҳ��һ��������ģ�������ר�ñ�����(ASSP)����Ҫ�����봦�����Ľӿڡ���SmartFusion�У�ģ������봦������FPGA������һ����ģ������У�Ԥ����ӿڿ���ʵ�ָ��������ȡ��������������ʹ�ò�����ֱ�۵�ͼ�θ�ʽ�����տɻ���ʺ������������Ա��ȫ��һ����ģ�����öԻ���

������һ��Ƕ��ʽ���������

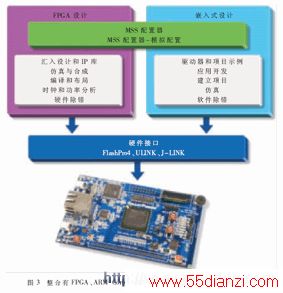

��������Ŀǰ��������������������Աһ�������������Ҫ��������������̣�������һ�ֱ������������Ա�������ͨ�ķ�����ͼ3Ϊ������ģ��ṹ��

��������Ƕ��ʽ�����Ա����һ���Dz鿴 MSS������ ��ѡ�����裬Ȼ�������������Լ��ı�I/O���ԡ�����Ҫ���ǣ����Ը����û���ѡ���Զ����ɴ洢��ӳ�����ѡ������Ҫ��ȫ���̼�������һ�������Ƕ��ʽ�����Ա���ѡ������GNU��Keil��IAR�ȹ��ߵı���������������ڡ�ʵ���ϣ�����ʹ�������κ���һ��ҵ�������IDE�У��������ṩMSS��������

��������������������⡢ϵͳ��ʼ�����������붼���Զ������ģ����Ϊ�����Ա��ʡ�˴�����ʱ�䣬���ػ���̫�ྫ�������ⲿ����ƣ��Ӷ�������ʱ������Ӧ�ÿ�����

����MSS������GUI���������������ܹ�ģ��ʾ��ͼ����������߶�Ƕ��ʽ��FPGA���������Ա��˵���Ƚ���ӱ������ͼ��ֱ���Խ������������������Ա˳����ѧϰ��ͬʱ����ÿ���˵�Ҫ��

����FPGA�����Ա��������������������ϵͳ��Ҳ��������һ����Ƕ��ʽ�����Ա��������������ϵͳ����ʱ��ֻ�����һ�ּ��ļ���ʽ�������Ա֮�䴫��MSS���ã����ش������������Ŀ��ʵ���ϣ�FPGA�����Ա��Ҫ�˽�MSS���õ�Ψһ������������FPGA�ܹ������ӡ�FPGA�����Ա����ܹ�������SmartDesign IPģ�������Ķ����������������ǻ�������봦����������������RTL�����������а�����ȫ��㷺��ʱ����ʷ����Ĵ�ͳFPGA������̡�

���Ĺؼ��֣��������� DSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����