0 引 言

伪噪声序列(PN序列)可应用于扩频 通信 、信息加密、计算机仿真等领域。PN序列发生器需要一个随机信号源和一系列的离散、量化算法及其硬件实现技术。确定性的混沌可以复制,具有长期不可预测性,且很难区分一个信号是来自于非确定性系统还是 混沌系统 。因此,混沌满足密码系统设计的基本原则,利用混沌系统作为PN序列的信号源已引起了国内外学者的广泛关注与研究。

基于 LogistIC 映射产生PN序列已有不少研究。文献[7]利用模拟电路研究了其实现技术,由于混沌对初值和参数的敏感性,两个模拟电路实现的PN序列,其电路参数不可能完全匹配,且受环境条件的变化而出现失配现象,很难保证保密通信或信息加密中两个PN序列的完全同步。因此,近年来开展了基于数字电路(如 FPGA )的PN序列的实现研究,但现有的研究中大多进行仿真实验,无法保证硬件实际输出PN序列的产生及其性能的测试。为此,基于FPGA技术,利用Logistic混沌映射作为随机信号源对实现PN序列的硬件进行了深入研究,提取Logistic数值序列中二进制数的某一位bi(bi∈{0,1})为PN数字序列,实验中获得了硬件输出序列,并通过一个串口通信电路对硬件输出序列进行取样,对其进行序列统计性能分析。分析结果表明,基于Logistic的PN序列性能良好,满足PN序列测试的标准。

1 Logistic映射

Logistic方程如下:

![]()

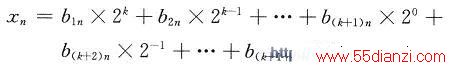

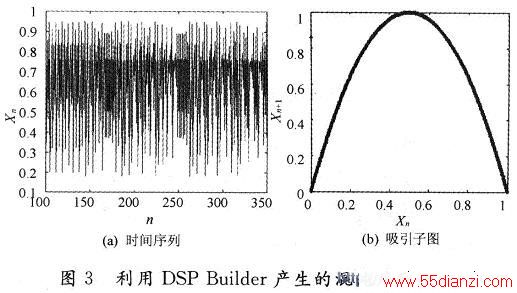

式中:Xn∈(0,1);μ∈(0,4),当μ取值[3.571 448,4]时,Logistic映射进入混沌态,并表现出复杂的动力学特性。在此取μ=4,令Xn的初值Xo=O.312 5,则xn的时间序列和吸引子相图如图1所示。

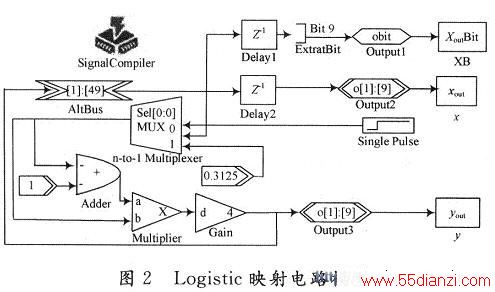

2 Logistic映射的电路设计及时间序列的量化

DSP Builder。将Matlab和Simlalink系统级设计工具的算法开发、仿真和验证功能与VHDL综合、仿真和开发工具整合在一起,实现了这些工具的集成,将系统级设计的实现与DSP算法的开发相链接,涵盖了算法和存储功能等基本操作。可利用DSP Builder模块迅速生成算法硬件电路,并转成VHDL语言,大大缩短了FPGA的设计周期。图2为Logistic的DSP Builder电路实现模型。

图2中为消除毛刺,在各输出端加入了一个延时器。其中,xout为Xn+1的时间序列;yout为其延时一个时钟周期后的输出,即Xo。xout与yout都是以二进制数表示的一系列小数(xn∈(0,1)),可表示为:

因为时间序列Xn的数值是用二进制数表示的,随着迭代的不断进行,Xn将随之变化,此时其二进制表示中的某一位(O或1)也随之变化。因此可以提取Xn时间序列中某一位二进制位作为量化值,当Xn的时间序列值随时间变化时即生成一PN序列。图2中的XoutBit为PN序列的输出端,它取自Xn二进制数表示中的第9位。后面的分析表明,这种量化方法同样具有很好的混沌性能和随机性。

为了验证图2电路模块的正确性,对Logistic的模块电路进行仿真,其时间序列和吸引子如图3所示。比较图3和图1发现,利用DSP Builder设计的电路有效地实现了Logistic映射的功能。

3 基于FPGA的PN序列实现

图2中,xout与yout具有相同的k及l值,k=1,l=9,即k+l=10。因为所使用的FPGA开发板自带THS5651DA转换器接受的是10引脚数据,k+l=10可实现匹配。尽管xout在最后输出前转成了10位长度,但在整个内部运算环节,是50位长度的,有限字长明显大于10,这样可以最大限度地保持精度,减少有限字长效应带来的误差,有效实现混沌的非周期特性。

理论上混沌序列是非周期的,但因为在使用有限字长表示混沌状态的情况下,加上运算结果的近似化,混沌序列最终会演化为一个周期序列。但是可以通过加长有限字长来延长周期。从实用的角度看,只要设计得好,映射和分叉参数选择合适,所产生的序列周期将足够长,序列的相关特性将足够好,可用的序列数量将足够多,可认为位转换就已够用,因为通信的时间不可能无限长。研究还发现,混沌映射产生的有限字长周期序列具有正的最大LyaPLLnov指数。

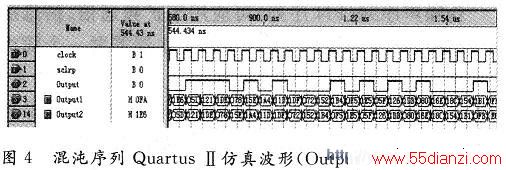

将图2所示的图形化模块通过“Signal Corepiler”直接转化为硬件描述语言,再利用QUARTusⅡ进行编译,其仿真时序图见图4。其中,Output为抽取的混沌数字PN序列,即图2中的XoutBit;Outputl和Output2分别为Xn+1和Xn。

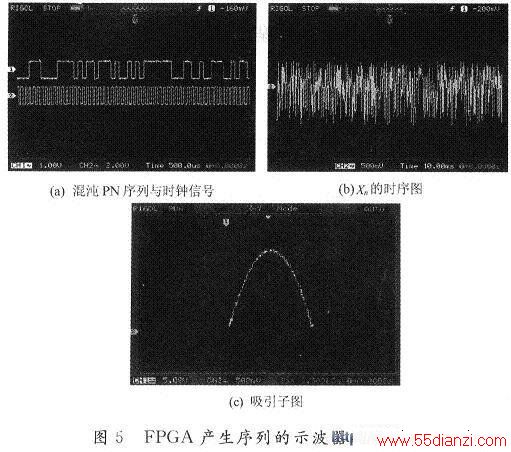

把工程文件在CycloneⅡ的EP2C35F484C8进行编译和引脚分配并下载到该芯片进行硬件实验,从数字示波器上观察到的PN序列如图5(a)所示。为了验证硬件实现的精度,通过THS5651芯片对得到的混沌数字信号进行D/A转化,再通过示波器观察其时间序列和吸引子,如图5(b),图5(c)所示。

4 PN序列随机性分析

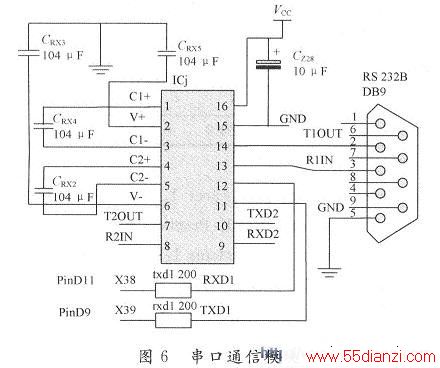

为了对硬件输出的PN序列进行性能测试,首先通过一个串口 通信 模块电路对 FPGA 输出的数字PN序列进行采样,然后利用计算机对其进行随机性能分析。这里采用的FPGA开发板其内核为CycloneⅡ的EP2(235F484C8,外围电路提供了USB口、并行I/O以及串口等一系列可供用户选择的端口。抽取Xn二进制表示的小数部分的第9位作为比特序列,并通过串口来实时获得该位在一定时间段t内的所有值,其串口通信模块电路如图6所示。

为了确保计算机在接收该序列时不出现比特丢失现象,可预先向计算机发送一组周期序列来保证数据的可靠性。假设串口传输波特率为9 600,系统晶振为20 MHz,为了得到整数倍的分频,可根据公式:

n=(20×106×k)/9600

令k=3,则可得出n为6 250。其中,比例因子k可通过锁相环来获得。上述两步骤可通过在QUARTusⅡ中添加锁相环代码与分频器代码实现。此时,让系统时钟T=1/9 600再经过二分频后通过串口输出,如果在接收端收到“01010”的周期序列,则表明FPGA与计算机之间的通信无问题。

5 PN序列随机性能分析

5.1 频率测试(Frequency Test)

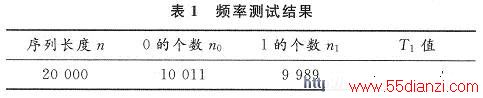

该测试可用来判断序列当中0和1的个数是否近似相等,若近似相等,则符合随机序列的必要条件。令n0,n1分别代表0与1的个数;n代表序列s的长度。

该统计方程为:

T1=(n0-n1)2/n

若n≥lO,则T1近似符合1维自由度的x2分布。

对采集到的PN序列进行自由度为l的x2检验,取显著性水平α=0.05,可以从标准表中查到显著性水平a=O.05的x2值为3.84。如果T1值小于3.84,则该序列通过测试。n0,n1和T1的测试值如表l所示,由此可知,该序列的T1值远小于3.84,通过测试。

5.2 串列测试(Serial Test)

该测试可用来判断序列中00,01,10,11子序列的个数是否近似相等。若近似相等,则符合随机序列的必要条件。令n0,n1分别代表0与1的个数,而n00,n01,n10,n11分别代表s序列中00,01,10,11的个数。由于n00+n01+no+nll=n-l,该统计方程为:

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术