微处理器中断接口

像请求处理器提供服务的所有外部器件一样,CPLD 也具有向微处理器发出中断的功能。CPLD 必须能够在完成数据采集操作之后向微处理器发出中断。设计人员可以为来自 CPLD 的中断请求设置优先级,并可选择该中断是否唤醒处于断电状态的处理器。

微处理器操作模式接口

CPLD 是否能识别处理器的操作状态取决于系统微处理器。有些微处理器提供表示当前操作模式的外部引脚。CPLD 可能会识别出处理器的当前操作状态,并且确定是否向处理器发出执行等待中断的请求,这取决于 CPLD 和微处理器的设计。例如,如果 CPLD 接收到低优先级中断,而处理器无需从低功耗状态转至其他状态,则 CPLD 可以创建一个寄存器以指示将中断挂起。然后,当处理器苏醒时,可由微处理器读取挂起中断的寄存器。

优点

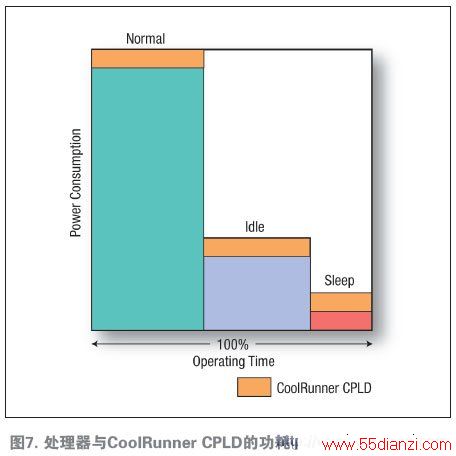

图 6 和图 7 所示为可在一种典型电池供电器件中实现的节电效果;其中图 7 所示为使用先进的低功耗 CPLD,图 6 所示为使用独立的微处理器设计。与通过延长微处理器低功耗模式所实现的节电效果相比,CPLD 的功耗要求微不足道。典型低功耗 CPLD 的待机电流约为 100μA。操作功耗取决于应用和时钟频率。对于充满 16 位计数器和 50MHz 时钟的 64 宏单元的 CPLD 来说,ICC 约为 10mA。请注意,所实现的实际节电效果取决于系统设计,包括微处理器类型和 CPLD 设计。

结论

设计 功耗 敏感型应用不仅涉及使用软件进行电源管理,还涉及运用硬件设计技巧。通过设计低功耗 CPLD 来延长微处理器的低功耗操作状态,可以显著降低系统功耗。当今市场上的最新 CPLD 可以为任何最终应用提供低功耗和高速度的灵活组合应用。

参考文献

《Intel StrongARM SA-1110 微处理器开发手册》,2000 年 6 月。

《摩托罗拉半导体应用指南》之“DragonBall 电源管理”,摩托罗拉公司,1998 年。

《Geode GX1 处理器系列低功耗集成 x86 解决方案》,National SEMIconductor 公司,2000 年 10 月。

Turley, Jim:《用于消费型电子设备、PDA 和通信的微处理器》。

《微处理器报告》,1999 年 9 月。

《第 27 期微处理器/控制器年度报告》之“EDN 访问”,2000 年 9 月。

本文关键字:处理器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术