目前,对高速通信与超快计算的需求正与日俱增。有线和无线通信标准的应用随处可见,数据处理架构每天都在扩展。较为普遍的有线通信方式是以太网(LAN、WAN 和 MAN 网络)。手机通信是最为常见的无线通信方式,由应用了 DSP 的架构实现。电话作为语音连接的主要工具,目前正在不断满足日益增强的语音、视频和数据要求。

系统设计人员在创建架构时不仅需考虑三网合一模式这一高端需求,还需满足以下要求:高性能;低延迟;较低的系统成本(包括 NRE);可扩展、可延伸架构;集成现成 (OTS) 组件;分布式处理;支持多种标准和协议。

这些挑战涉及到两个主要方面:有线或无线架构中计算平台/箱间的连接以及这些平台/箱中的具体计算资源。

计算平台间的连接

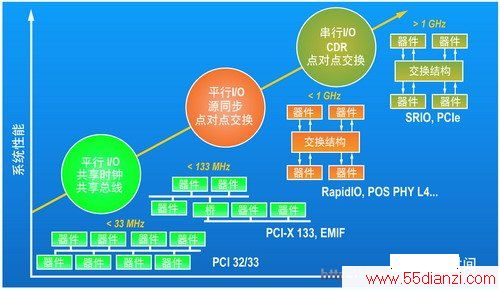

基于标准的连接目前较为普遍。并行连接标准(PCI、PCI-X、EMIF)可以满足现在的需求,但在扩展性和延伸性方面略显不足。随着基于包处理方式的出现,使用趋势明显偏向高速串行连接(见图1)。

图1 串行连接趋势

台式电脑和网络工业已采用了 PCI Express (PCIe) 和千兆位以太网/XAUI 等标准。不过,无线架构中数据处理系统的互连要求略有不同,其特点是:低引脚数;背板芯片对芯片连接;带宽和速度可扩展;DMA 和信息传输;支持复杂的可扩展拓扑;多点传输;高可靠性;绝对时刻同步;服务质量 (QoS)。

串行 RapidIO (SRIO) 协议标准可轻易满足并超过大多数上述要求。因此,SRIO 成了无线架构设备中数据平面连接的主要互连。

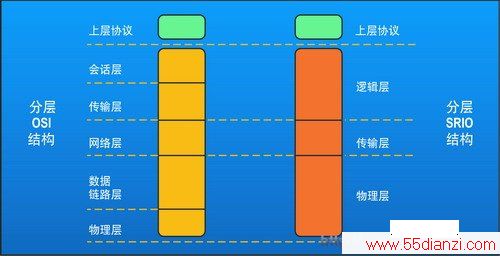

图2 SRIO网络构建模块

SRIO 网络围绕两个基本模块构建而成:端点和交换机(见图2)。端点对包进行源端(source)和宿端 (sink) 处理,而交换机在端口间传送包,对其不加解析。SRIO以一个三层架构层级指定(见图3):

图3 分层SRIO架构

SRIO - 优势前景

以 3.125Gbps 运行的 4 通道 SRIO 链路可以提供 10Gbps 的流量,且保证数据完整性。由于SRIO类似于微处理器总线(存储器和器件寻址,而非 LAN 协议的软件管理),因此包处理是通过硬件实现的。这意味着可大幅削减 I/O 处理方面的额外开销,降低延迟并增加系统带宽。但与多数总线接口不同,SRIO 接口的引脚数较少,带宽在链路为 3.125Gbps 的基础上可继续扩展。

平台中的计算资源

如今的应用对处理资源的数量要求较高。基于硬件的应用发展迅猛。压缩/解压缩算法、反病毒和入侵监测等防火墙应用以及要求 AES、三倍 DES 和 Skipjack 等加密引擎的安全应用起初都是通过软件实现的,但目前都已转为硬件实现。这就需要带宽和处理能力能够实现共享的大型并行生态系统。系统需要使用 CPU、NPU、FPGA 或 ASIC,从而实现共享或分布式处理。

在构建能够适应未来发展变化的系统时,需考虑所有这些针对具体应用的要求,对计算资源的要求包括:

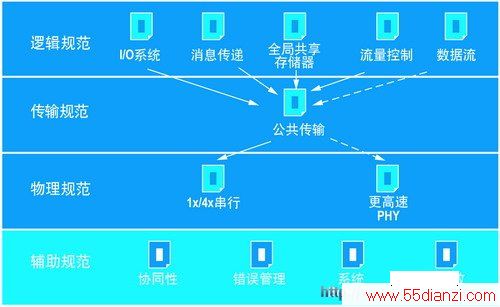

SRIO 规范(见图4)对基于包的分层架构进行了定义,可支持多个域或市场区间,从而有利于系统架构设计师设计新一代计算平台。通过将 SRIO 用作计算互连,可轻松实现以下功能:使架构独立;部署可靠性为运营商级的可扩展系统;实现高级流量管理;提供高性能、高流量。此外,由大批供应商构成的生态群使得 OTS 部件与组件的选择十分容易。

图4 SRIO规范

SRIO 为基于包的协议,该协议支持:通过基于包的操作(读、写、消息)移动数据;I/O 非连贯功能和缓存连贯功能;通过支持数据流、数据分区和重组功能而实现高效互通和协议封装;通过启用数百万个流而实现流量管理框架,支持 256 流量级别和有损操作;流控制,支持多个事务请求流,提供 QoS;支持优先级别,从而可缓解带宽分配和事务顺序等问题,并避免死锁;支持拓扑,通过系统发现、配置和维护支持标准(树状和网格)与任意硬件(菊花链)拓扑,包括支持多个主机;错误管理和分类(可恢复、提醒和致命性)。

www.55dianzi.com

Xilinx针对SRIO的IP解决方案

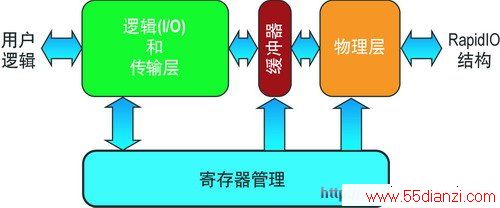

用于 SRIO 的 Xilinx 端点 IP 解决方案针对 RapidIO 规范 (v1.3) 而设计。用于 SRIO 的完整 Xilinx 端点 IP 解决方案包括以下部分(见图5):

图5 用于SRIO的Xilinx端点IP构架

用于 SRIO 的整个 Xilinx 端点 IP LogiCORE 解决方案已全面经过测试,硬件验证也已进行,目前正在就与主要 SRIO 器件供应商之间的协同工作能力接受测试。LogiCORE IP 通过 Xilinx CORE Generator软件 GUI 工具提供,该工具允许用户定制波特率和端点配置,并支持流量控制、重发送压缩、门铃和消息接发等扩展功能。这样,用户便可创建一个灵活、可扩展的定制 SRIO 端点 IP,对自己的应用进行优化。

Virtex-5 FPGA计算资源

用于 SRIO 的 Xilinx 端点 IP 可确保在使用 SRIO 协议的链路双方间建立高速连接。在最小的 Virtex-5 器件中,IP 仅占用不到 20% 的可用逻辑资源,因此可确保用户设计使用大多数逻辑/存储器/I/O,集中实现系统应用。

逻辑模块

Virtex-5 逻辑架构带有基于 65nm 工艺的六输入查找表 (LUT),可提供最高的 FPGA 容量。进位逻辑经过改进后,该器件的性能比之前的器件高出 30%。由于所需 LUT 减少,该器件的功耗明显降低,且具备高度优化的对称布线架构。

存储器

Virtex-5 存储器解决方案包括 LUT RAM、BLOCk RAM 及与大型存储器进行接口的存储器控制器。Block RAM 结构包括预制 FIFO 逻辑,即可用于外部存储器的嵌入式检错和纠错 (ECC) 逻辑。另外,Xilinx 可通过存储器接口生成器 (MIG) 工具向系统设计中的例化存储器控制器模块提供综合设计资源。这样,用户便可利用经过硬件验证的解决方案,并将精力集中于设计中的其他关键部位。

并行和串行 I/O

SelectIO技术几乎可在设计中实现客户所需的任何并行源同步接口。使用 SelectIO 接口,可方便地针对 40 多种不同的电气标准创建符合行业标准的各类接口,也可创建专用接口。SelectIO 接口提供的最大速率为700Mbps(单端)和1.25Gbps(差分)。

本文关键字:能力 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术