所有Virtex-5 LXT FPGA都集成有一个 GTP 收发器,运行速度介于 100 Mbps 到 3.2Gbps 之间。另外,GTP 收发器在业界属于最低功率 MGT 之一,每个收发器的功率小于 100mW。引入用来简化设计的成熟设计技术和方法后,高速串行设计的流程变得简单快捷。

另外,通过新设计工具(RocketIO收发器向导与 IBERT)和新硅片性能(TX 和 RX 均衡与内置伪随机位序列 (PRBS) 生成器和检查器),可以开发移植架构的各种功能和优势,从并行 I/O 标准到 30 多种串行标准及新兴的串行技术。

DSP 模块

每个 DSP48E Slice 可提供 550MHz 的性能水平,允许用户创建要求单精度浮点性能的各类应用,如多媒体、视频和图像应用以及数字通信。这扩展了器件的功能,使其优于之前的器件,同时还提供了功率优势,动态功耗的降低幅度超过了 40%。Virtex-5 FPGA 中还增加了 DSP48E Slice 的数量,这些模块相对于可用逻辑资源及存储器的比率从而得到了优化。

www.55dianzi.com

集成 I/O 模块

所有 Virtex-5 LXT FPGA 器件都具备一个端点模块,用来实现 PCIe 功能。通过这种硬 IP 端点模块,只需简单地重新进行配置即可轻松地从 x1 扩展至 x2 和 x4 或 x8。该模块(x1、x4 和 x8 链路)已通过严格的 PCI-SIG 兼容性和协同工作能力测试,用户可放心用于 PCIe。

另外,所有 Virtex-5 LXT FPGA 器件均装有三态以太网媒体访问控制器 (TEMAC),速度可达 10/100/1000Mbps。该模块可提供专用以太网功能,再结合 Virtex-5 LXT RocketIO 收发器和 SelectIO 技术,可方便与许多网络器件进行连接。

利用针对 PCIe 和以太网的这两种模块,可以创建一系列定制包处理和网络产品,这些产品可大幅降低资源利用率和功耗。通过使用 Xilinx FPGA 中提供的这些各式资源,可以轻松创建并部署智能解决方案。

SRIO 嵌入式系统应用

可以考虑围绕基于 x86 架构的 CPU 构建一个嵌入式系统。CPU 架构已高度优化,可轻易满足要求玩弄数字于股掌的各类应用。用户可以轻松地在使用 CPU 资源的硬件和软件中实现各类算法,以执行不需要进行大量乘法运算的电子邮件、数据库管理以及文字处理等功能。性能以每秒钟所产生的指令/运算为数百万还是数十亿来衡量,而效率通过完成特定运算所需的时间/周期来衡量。

需进行大量定点和浮点运算的高性能应用在处理数据时需花费较长时间。这方面的示例包括信号过滤、快速傅里叶变换、矢量乘法和搜索、图像/视频分析和格式转换以及简单的数字处理算法。在 DSP 中实现的高端信号处理架构可轻松执行这些任务,并可优化此类运算。这些 DSP 的性能以每秒钟进行多少次乘法和累加运算来衡量。

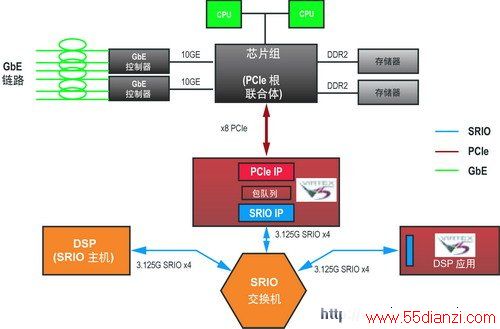

用户可以方便地设计使用 CPU 和 DSP 的嵌入式系统,以充分利用两种处理技术。图 6表示使用 FPGA、CPU 和 DSP 架构的系统示例。

高端 DSP 中的主要数据互连为 SRIO。x86 CPU 中的主要数据互连为 PCIe。如图 6 所示,用户可轻松部署 FPGA 以扩展 DSP 应用或对离散数据互连标准(如 PCIe 和 SRIO)进行桥接。

图6 基于CPU的可扩展、高性能、嵌入式系统

在图 6 所示系统中,PCIe 系统由根联合体(Root Complex)芯片组托管。SRIO 系统由 DSP 托管。32/64 位 PCIe 地址空间(基址)可智能化地被映射至 34/66 位 SRIO 地址空间(基址)。PCIe 应用可通过存储器或 I/O 读写与根联合体进行通信。这些事务会通过 NRead/NWrite/SWrite 轻松映射至 SRIO 空间。

在 Xilinx FPGA 中设计此类桥接功能很简单,因为这些 Xilinx 端点功能模块、PCIe 和 SRIO 的后端接口都很相似。这样,“包队列”模块便可执行从 PCIe 到 SRIO 或反方向的交叉任务,从而建立可穿越两个协议域的包流。

SRIO DSP 系统应用

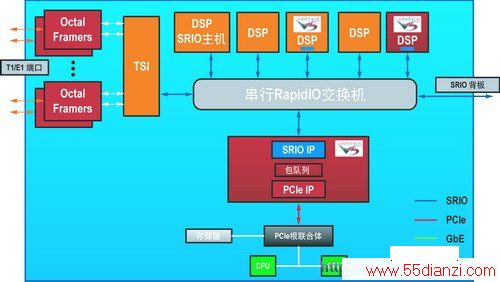

在 DSP 处理为主要架构要求的应用中,系统架构可按图 7 进行设计。

图7 DSP密集型阵列

基于 Virtex-5 FPGA 的 DSP 处理与系统中的其他 DSP 器件结合即可构成智能 协处理 解决方案。如果使用 SRIO 作为数据互连,整个 DSP 系统解决方案就可以方便地进行扩展。此类解决方案能够适应未来的发展变化,提供了延伸性,而且受多种形状因子的支持。在 DSP 密集型应用中,通过将相应处理任务卸载至 x86 架构中可实现快速数字分析或数据处理。使用 Virtex-5 FPGA 可轻易地连接 PCIe 子系统和 SRIO 架构,从而实现高效功能卸载。

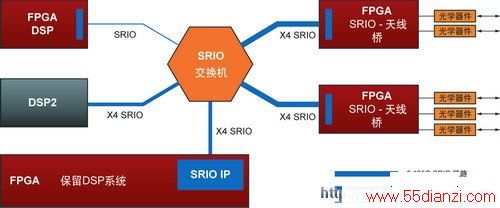

SRIO 基带系统应用

现有 3G 网络正在以较快的步伐迈向成熟,OEM 也在为缓解特定容量和覆盖率问题而部署新的形状系数。要解决此类特殊问题,对市场趋势做出评估,基于 FPGA 的 DSP 架构是理想选择,该架构将 SRIO 用作数据层面标准。另外,早期 DSP 系统可快速升级,变为快速、低功耗 FPGA DSP 架构,从而获得可扩展性优势。

如图 8 中的系统所示,您可以对 Virtex-5 FPGA 进行设计,以满足现有对天线流量的线速率处理需求,还可通过 SRIO 提供与其他系统资源间的连接。现有早期 DSP 应用的固有并行连接速度较慢,因可应用于 Virtex-5 FPGA 的 SRIO 端点功能的存在,移植这些应用极为方便。

图8 可扩展基带上行链路/下行链路卡

www.55dianzi.com

结语

SRIO 正出现在大量新应用中,主要以有线和无线应用中的 DSP 为中心。在 Xilinx 器件中实现 SRIO 架构的主要优势包括:整个 SRIO 端点解决方案的可用性;灵活性和可扩展性,便于使用同样的硬件和软件架构制成不同级别的产品;通过新 GTP 收发器和 65 nm 技术实现了低功耗;通过 CORE Generator 软件 GUI 工具轻松进行配置;与业界领先的供应商间的硬件协同工作能力经过了验证,支持其器件上的 SRIO 连接; 通过使用 PCIe 和 TEMAC 等集成 I/O 模块,实现了系统集成,从而降低了总体系统成本。

另外,Virtex-5 FPGA 所具备的 DSP 资源可在功耗、性能和带宽方面满足现有早期 DSP 系统的要求。更多优势还体现在系统集成方面,诸如以太网 MAC 的功能模块、用于 PCIe 的端点模块、处理器 IP 模块、存储元件及控制器等等。另外,由于 IP 核的详尽列表支持在 FPGA 中进行多种源整合,可以大大节省总体系统成本。

本文关键字:能力 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术