引言

Nios II 处理器是ALTEra公司设计的一款基于FPGA的32位RISC嵌入式软核处理器,具有32位指令集、数据通路及地址空间,是其可编程系统芯片( SOPC )的核心。Nios II系统采用Altera公司设计的一套Avalon总线交换结构,Avalon总线上的所有信号都与系统时钟同步且地址、数据和控制信号使用独立的端口;支持各种传输方式;采用从端口仲裁机制,对于有多个主设备的系统可以提高系统的吞吐量。

采用基于FPGA 的Nios II软核处理器很容易在嵌入式系统设计中实现 多处理器系统 。在这样的多处理器系统中,一般外部处理器做主处理器,Nios II处理器为从处理器,两个处理器有共用的存储器可以进行数据交互。本文将通过对Nios II 系统启动 的研究设计一方案,用外部处理器配置FPGA,加载程序代码到Nios II系统中的程序存储器中,最

终完成Nios II系统的启动。

在多处理器系统的启动方案

在多处理器系统中,为了降低成本,可以省去Nios II的一个非易失性存储器外设,如flash、EPROM等,Nios II处理器通过Avalon交换结构连接易失性存储器,一个外部主处理器及一些必要的接口外设。因此延迟Nios II的启动是必要的,解决办法是在Nios II系统中设计一启动延迟模块,把此模块的基址设为Nios II的复位地址。通过此模块,Nios II处理器上电复位后启动被延迟,直到数据被传输完毕,外部处理器通过启动延迟模块向Nios II发送一个可以开始进入程序存储器的指令,然后跳转到程序存储器开始执行,完成后续的设备初始化及应用程序的执行。

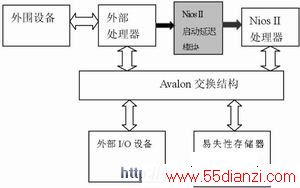

外部处理器通过时序转接桥连接在Avalon交换结构上和Nios II处理器共同构成的一个双处理器系统如图1所示。黑色箭头表示Nios II启动延迟模块是通过Avalon交换结构连接的。

图1 多处理器系统的启动方案结构

启动方案的硬件设计

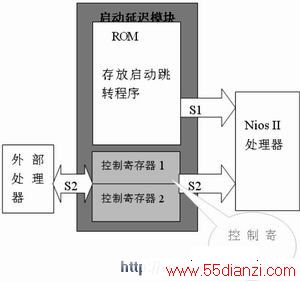

启动延迟模块如图2所示,它有两个从端口S1、S2:S1一端连接在启动延迟模块中的ROM单元上,另一端通过Avalon总线连接在Nios II处理器的指令主端口;S2一端连接在启动延迟模块的控制寄存器上,另一端通过Avalon总线连接在外部处理器和Nios II处理器的数据主端口。图2中箭头的方向表示数据的流向。

图2 Nios II启动模块的硬件结构

在此需做两点说明:

* 在启动延迟模块中有两个寄存器,这两个寄存器定义如下:

说明:控制寄存器1用于存放NiosII程序存储器中_start程序的入口地址。控制寄存器2中跳转标志位(31_1位保留) 。

www.55dianzi.com

这两个寄存器值由外部处理器来写入,其中偏移量为0的寄存器存放 Nios II 程序存储器中_start程序的入口地址,此值由外部处理器写入;偏移量为1的寄存器只用了第0位,其它位保留,当外部处理器配置好Nios II处理器系统后,会向此寄存器的第0位写入1,否则保持为0。

* ROM中的数据是外部处理器在配置FPGA的时候写入的,因此只要FPGA配置完成后,启动代码就存放进ROM中了。ROM的大小要根据启动程序代码的大小来决定,设计中应尽可能降低这段程序的代码存储量。

下边是用Verilog 硬件描述语言编写的启动延迟模块的硬件代码的主体框架结构:

//ROM读端口(S1):

boot_rom the_boot_rom

(

.cLOCk (s1_cl

k), file://s1_clk 为来自Avalon总线模块上的S1端口的时钟信号

.aclr (s1_reset), file://s1_reset 为来自Avalon总线模块上的S1端口的复位信号

.q (s1_readdata), file://s1_readdata 为流向Avalon总线模块的S1端口的32位数据

.address (s1_address) file://s1_address 为来自于Avalon总线模块的S1端口的地址

);

file://控 制寄存器读写端口(S2):

control_register the control_register

(

.clk (s2_clk), file://s2_clk 为来自Avalon总线模块上的S2端口的时钟信号

.reset (s2_reset), file://s2_reset 为来自Avalon总线模块上的S2端口的复位信号

.read (s2_read), file://s2_read 为来自Avalon总线模块上的S2端口的读使能信号

.write (s2_write), file://s2_write 为来自Avalon总线模块上的S2端口的写使能信号

.sChipselect (s2_chipselect), file://s2_chipselect 为来自Avalon总线模块上的S2端口的片选信号

.address (s2_address), file://s2_address 为来自Avalon总线模块上的S2端口的地址

.readdata (s_readdata), file://s2_chipselect 为流向Avalon总线模块上的S2端口的32位读数据

.writEDAta (s2_writedata) file://s2_writedata 为来自Avalon总线模块上的S2端口的32位写数据

);

启动方案的软件设计

启动方案的软件设计目标是当系统复位后,在外部处理器向Nios II程序存储器和数据存储器传输数据的过程中,Nios II处理器运行要受到外部处理器的控制。当一切就绪后,外部处理器发出一条释放Nios II处理器的命令,接下来Nios II处理器就可以正常运行了。

软件部分主要就是存放在启动延迟模块中ROM的代码,此代码主要是检测启动延迟模块中控制寄存器2的第0位是否为1。若为1,则跳转到控制寄存器1中所存储的地址处执行。若设控制寄存器的基址为CONTROL_REG_BASE,为了减少代码量,这段代码容易用Nios II的汇编指令来实现,代码部分在此从略。

www.55dianzi.com

最后本方案在我们自己设计的一块开发板上经过测试,能够正确完成 Nios II 处理器的启动。

结语

采用多处理器的系统虽然可以提高系统的性能,但传统的 多处理器系统 一般只出现在工作站及高端PC上,在嵌入式系统中由于其设计代价太高很少采用。本文设计了一种在多处理器系统中的Nios II软核处理器的启动方案,这个方案在外部处理器向Nios II的程序存储器和数据存储器加载数据时,可以控制Nios II处理器的启动。

参考文献:

1. Creating Multiprocessor Nios II SystEMS Tutorial.

2005

本文关键字:处理器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术