一、概述

提升机、电梯等设备的拖动系统通常采用可逆调速系统。晶闸直流可逆调速系统是典型的系统之一,常采用反并联的电枢可逆线路。这种线路有许多优点,如可实现可逆运行、回馈制动等,但会产生环流现象。环流有利弊,在有些场合,为了保证系统的安全,必须消除系统中的环流。所谓逻辑无环流系统就是在一组晶闸管工作时,用逻辑电路封锁另一组晶闸管的触发脉冲,使该组晶闸管完全处于阻断状态,从根本上切断环流通路。

二、逻辑无环流可逆调速系统及逻辑切换装置DLC

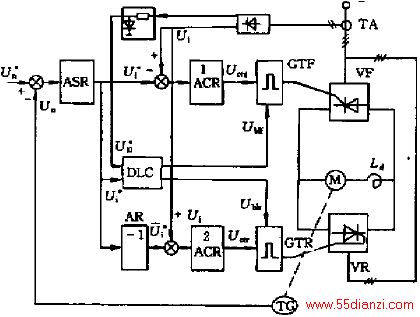

1、逻辑无环流可逆调速系统的组成

系统框图如图1所示。这是一个典型的逻辑控制无环流调速系统,系统关键是设置了一套无环流逻辑切换装置(DLC),它根据转矩极性信号UI*和零电流检测信号Ui0*,经逻辑判断出Ublf、Ublfr信号,分别控制两组触发装置GTF和GTR。

图1 逻辑无环流可逆调速系统结构框图

传统的逻辑控制无环流系统中,DLC通常由数字逻辑电路实现。随着具有数据运算功能及带有模拟量输入输出模块的PLC的出现,已经可用PLC实现转速给定、转速反馈及电流反馈;实现A/D、D/A转换;实现数字PI控制及数字滤波;实现数字触发等功能。本文主要讨论怎样用PLC从软件上实现DLC的功能。

2、DLC装置

(1)DLC的任务

在正组晶闸管VF工作时开放正组脉冲,封锁反组脉冲。在反组晶闸管VR工作时开放反组脉冲,封锁正组脉冲。

(2)DLC的工作要求

①DLC根据转矩极性信号UI*和零电流检测信号Ui0*经逻辑运算后发出逻辑切换指令。当UI*改变极性,且零电流检测器发出“零电流”信号时,允许封锁原工作组,开放另一组。

②DLC发出切换指令后需经过封锁时时间Tdb1才能封锁原导通组脉冲;再经过开放延时时间Tdt后才能开放另一组脉冲。通常Tdb1=3ms,Tdt=7ms。

③在任何情况下,两组晶闸管绝对不允许同时加触发脉冲,当一组工作时另一组触发脉冲必须被封锁。

(3)DLC的组成

根据系统对DLC的工作要求,DLC应由下列4部分组成,即电平检测、逻辑运算、延时电路和联锁保护。其中电平检测的功能是将模拟量转换成数字量供后续电路使用。

三、DLC装置的PLC实现

硬件实现的DLC装置是用集成运放器构成电平检测电路,用组合逻辑元件及一些分立电子元件构成其他部分,整个装置电路较为复杂,可靠性差。PLC具有较强的逻辑运算功能,在由PLC实现的DDC直流可逆调速系统中,为了实现DLC装置的功能,不需增加任何配件,只要利用PLC内部的软继电器等即可从软件上实现DLC的功能。PLC实现DLC装置功能的如下所述。

1、电平检测

电平检测电路包括转矩极性鉴别器DPT及零电流检测器DPZ,图2a、b分别是DPT与DPZ所要求的输入输出特性。

图2 DPT、DPZ的输入输出特性

由于DPT与DPZ的输入信号UI*、Ui0*易受干扰影响,为了避免误动作,电平检测器的继电特性应具有一定的环宽,通常为0.4V,以提高抗干扰能力。根据DPT、DPZ输入输出特性,可得流程框图如图3a、b所示。

图3 电平检测流程图

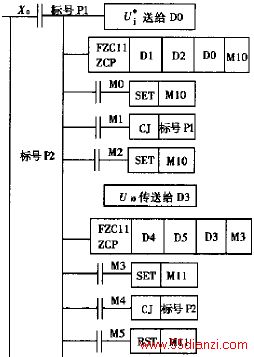

下面以FX2系列为 例说明如何实现DPT及DPZ的功能。设:转矩极性鉴别信号UI*已传送给娄据寄存器DO;DPT输入输出特性环宽数据-0.2及0.2已存入数据寄存器D1和D2;DPT输出状态UT由辅助寄存器M10保存。同理,零电流检测信号Ui0*已传送给数据寄存器D3;DPZ输入输出特性环宽数据0.2及0.6已存入数据D4、D5;DPZ输出关状态Uz由辅助寄存器M11保存。

实现图3流程的梯形图如图4所示,由此完成UI*、Ui0*的电平检测。

图4 电平检测梯形图

2、逻辑判断

通过对可逆调速系统正反向运行和起制动状态的具体分析,可得到如下逻辑控制要求:

![]()

![]()

设UF、UR的状态分别用辅助寄存器M12、M13表示。

3、延时电路

在逻辑运算判断部分发出切换指令UF、UR后,必须经过封锁延时Udb1和开放延时Udt才能执行切换命令。在数字逻辑电路的DLC装置中是在与非门前加二极管及电容来实现延时。用FX2系列PLC实现时,只要用其内部的1ms定时器即可达到延时目的。一般封锁延时取Udb1=3ms,此时封锁原导通组脉冲;再经过开放延时Udt=7ms开放另一组。若封锁延时与开放延时同时开始计时,则开放延时时间为3+7=10ms,设延时后的UF'、UR'状态分别用辅助寄存器M14、M15表示。

4、联锁保护

DLC装置的最后部分为逻辑保护环节。正常时,UF'与UR'状态总是相反的;一旦DLC发生故障,使UF'和UR'同时为“1”,将造成两组晶闸管同时开放,必须避免此情况。满足保护要求的逻辑真值表如下表。设DLC的输出信号由PLC输出端子Y0、Y1输出。

本文关键字:暂无联系方式电工文摘,电工技术 - 电工文摘