这里我们教大家使用ModelSim完成基本的HDL仿真。所应用的仿真代码是ModelSim自带的。安装了ModelSim后,可以在安装目录的examples/tutorials/verilog/basICSimulation下找到counter.v 和tcounter.v。其中counter.v是被验证设计,tcounter.v是Testbench。

仿真过程如下

1.打开ModelSim,首先建立一个新的Project,选择File->New->Project,

图1

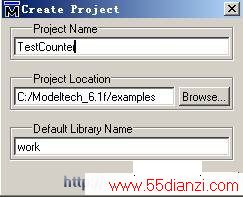

2. 在弹出的Create Project窗口中给Project任意起一个名字,并指定Project的目录(Project LOCation)。我们假设Project Name为TestCounter,创建的Library名为work(所有我们编译后的代码的模块将被放入到work库中)。如下图所示:

图2

3.点击OK后弹出添加HDL代码到Project的窗口,如下图:

图3

(

www.55dianzi.com

我们选择Add Existing File,假设$ModelSim是你的ModelSim的跟目录,则添加下面两个文件:

$ModelSim/examples/tutorials/verilog/basICSimulation/counter.v

$ModelSim /examples/tutorials/verilog/basicSimulation/tcounter.v

添加文件的窗口如下图所示

图4

Tcounter.v的源代码如下:

- module test_counter;

- reg clk, reset;

- wire [7:0] count;

- counter dut (count, clk, reset);

- initial // CLOCk generator

- begin

- clk = 0;

- forever #10 clk = !clk;

- end

- initial // Test stimulus

- begin

- reset = 0;

- #5 reset = 1;

- #4 reset = 0;

- end

- initial

- $monitor($stime,, reset,, clk,,, count);

- endmodule

counter.v的源代码如下:

- module counter (count, clk, reset);

- output [7:0] count;

- input clk, reset;

- reg [7:0] count;

- parameter tpd_reset_to_count = 3;

- parameter tpd_clk_to_count = 2;

- function [7:0] increment;

- input [7:0] val;

- reg [3:0] i;

- reg carry;

- begin

- increment = val;

- carry = 1'b1;

- /*

- * Exit this loop when carry == zero, OR all bits processed

- */

- for (i = 4'b0; ((carry == 4'b1) && (i <= 7)); i = i+ 4'b1)

- begin

- increment[i] = val[i] ^ carry;

- carry = val[i] & carry;

- end

- end

- endfunction

- always @ (posedge clk or posedge reset)

- if (reset)

- count = #tpd_reset_to_count 8'h00;

- else

- count <= #tpd_clk_to_count increment(count);

- /*****************************************************************

- Use the following block to make the design synthesizable.

- always @ (posedge clk or posedge reset)

- if (reset)

- count = 8'h00;

- else

- count <= count + 8'h01;

- ******************************************************************/

- Endmodule

(

www.55dianzi.com

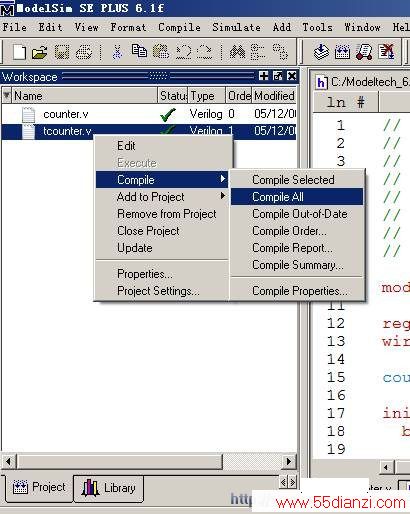

我们在WorkSPACe下单击右键选择Compile->Compile All,编译上述两个文件,如下图所示:

图5

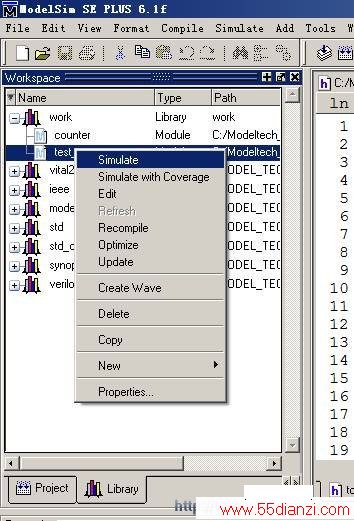

从tcounter.v的源代码为我们看到Testbench的模块名叫test_counter,我们切换WorkSpace到Library,选择work库下的test_counter,单击鼠标右键选择simulate,如下图所示。

图6

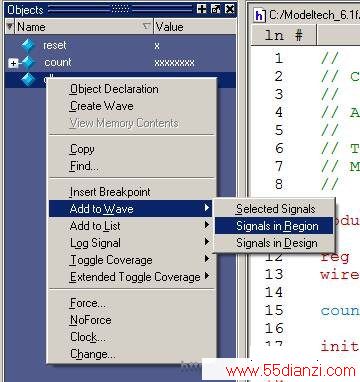

我们在弹出的Objects窗口中单击鼠标右键,选择Add to wave->Signals in Region,如下图所示:

图7

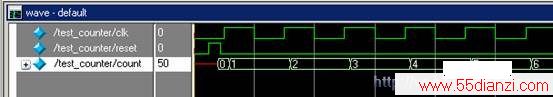

我们将仿真时间改为 1 us,并单击菜单中的Run按钮,并如下图所示:

图8

(

www.55dianzi.com

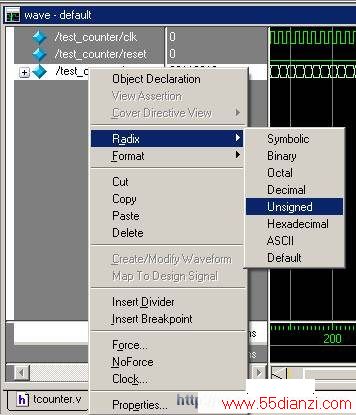

我们在wave窗口中选择count,将其改为无符号整形显示。选择count,单击鼠标右键,选择Radix->Unsigned,如下图所示:

本文关键字:暂无联系方式电脑-单片机-自动控制,电子学习 - 基础知识 - 电脑-单片机-自动控制