OLED具备自发光、不需背光源、对比度高、厚度薄、视角广、反应速度快、可用于挠曲性面板、使用温度范围广、构造及制程较简单等优异特性,被认为是下一代的平面显示器新兴应用技术。目前OLED的驱动大部分都是基于STM系列 ARM芯片和传统FPGA芯片。为适应Xilinx最新平台Zynq的人机交互需要,提出一种基于Zynq的OLED驱动设计方法。文章阐述了OLED的特性和SPI控制方式,给出了设计流程和硬件电路图。利用Zynq的PL部分完成了OLED驱动的IP核,利用Zynq的PS部分实现了OLED的驱动程序设计。通过AXI总线实现PL和PS的通信。最后通过测试程序,实现了字母、数字和点阵图像的实时显示。解决了基于Zynq器件在广电仪器和电力仪表仪器中人机交互的工程技术,具有集成度高、可移植性强和通用性好等优点。

1 引言

随着近几年嵌入式技术的飞速发展和广泛应用,人机交互成为嵌入式设备的迫切需要。为适应Xilinx最新平台Zynq的人机交互需要,提出一种基于Zynq的OLED驱动设计方法。

有机发光二极管(OrganIC Light-EMItting Diode,OLED)由于同时具备自发光、不需背光源、对比度高、厚度薄、视角广、反应速度快、可用于挠曲性面板、使用温度范围广、构造及制程较简单等优异特性,被认为是下一代的平面显示器新兴应用技术。

Xilinx最新平台Zynq将处理器的软件可编程能力与FPGA的硬件可编程能力实现完美结合,以低功耗和低成本等系统优势实现良好的系统性能、灵活性和可扩展性。

目前OLED的驱动大部分都是基于STM系列ARM芯片和传统FPGA芯片。在Zynq上,Xilinx提供了Linux演示实例,但无裸机源码,无法满足实时性比较强的工程实际需求。

文章详细阐述了基于Zynq的OLED驱动设计步骤和方法,并且在基于Zynq的开发板ZedBoard上实现了实时显示字母、数字和点阵图像,为Zynq在仪器仪表领域实现人机交互提供了技术支撑。

2 OLED驱动设计流程

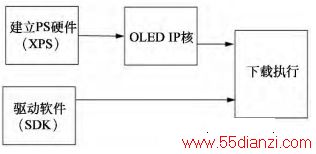

Zynq是一个ARMPS+PL结构,其中PL部分就是传统意义的FPGA,可以方便地定制相关外设IP,也可以进行相关的算法设计,和使用普通FPGA完全一样。如果不使用PL,Zynq的PS部分和普通的ARM开发一样。Zynq最大的特点是可以利用PL部分灵活地定制外设,挂在PS上,而普通的ARM,外设是固定的。因此,Zynq的硬件外设是不固定的,这也是Zynq灵活性的一个表现。OLED在Zynq上是连接在PL上,因此需要把OLED对应引脚挂在PS的硬件上,然后设计OLED IP核,再通过SDK设计驱动程序,OLED驱动设计流程如图1所示。

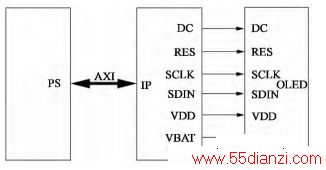

ZedBozrd控制OLED的主要方法是:自行设计一个IP核,对OLED的6个控制信号和电源信号进行逻辑设计和引脚约束,通过AXI总线,把OLED的IP核和PS联系起来。在PS部分编写相应的驱动程序,即可实现对OLED的控制,如图2所示。

图1 OLED驱动设计流程

图2 OLED系统设计图

因此,要实现OLED显示功 能,主要做以下几个方面工作:设计Zynq硬件系统(PS部分)、设计自己的IP核和PS部分驱动程序设计。

3 建立Zynq硬件系统和OLED IP核

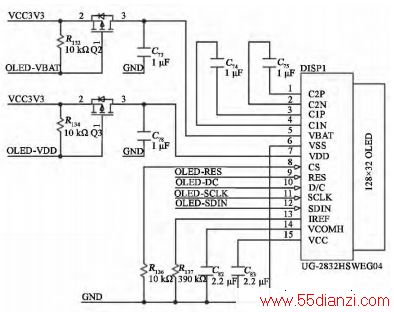

Zynq的开发板ZedBoard上使用Inteltronic/WiseChip公司的OLED显示模组UG-2832HSWEG04,分辨率为128×32,是一款单色被动式显示屏,驱动电路采用所罗门科技的SSD1306芯片。具体电路如图3所示。根据原理图可知,ZedBoard开发板使用的OLED采用SPI方式控制,SPI模式使用的信号线和电源线有如下几条:

RST(RES):硬复位OLED;

DC:命令/数据标志(0,读写命令;1,读写数据);

SCLK:串行时钟线;

SDIN:串行数据线;

VDD:逻辑电路电源;

VBAT:DC/DC转换电路电源。

在SPI模式下,每个数据长度均为8位,在SCLK的上升沿,数据从SDIN移入到SSD1306,并且是高位在前的。

图3 OLED原理图

Zynq的硬件系统是指在PL中配置相关外设,挂载到PS中,作为PS部分的外设使用。OLED驱动主要用到6个IO口,在生成硬件系统时,只需要利用Xilinx的嵌入式工具XPS生成最小硬件系统,然后把OLED的相关引脚添加到最小硬件系统中。主要过程如下:

(1)根据芯片型号,根据XPS工具设计流程,生成Zynq的最小硬件系统。

(2)在最小硬件系统中,添加外设IPmy_oled,把OLED的SPI引脚添加到工程中。添加一个6位寄存器,每位和SPI引脚对应。

(3)my_oleDIP核逻辑设计主要完成IP核引脚添加、端口映射和用户逻辑功能。首先要对设计的IP核添加引脚,在系统生成的MPD文件中,添加OLED的相关引脚端口和方向信息。

在MPD文件中,在PORT下添加OLED的相关引脚和方向信息,具体代码如下:

PORTDC=“ ”,DIR=O

PORTRES=“ ”,DIR=O

PORTSCLK=“ ”,DIR=O

PORTSDIN=“ ”,DIR=O

PORTVBAT=“ ”,DIR=O

PORTVDD=“ ”,DIR=O

(4)在系统生成的my_oled.vhd文件中,用VHDL语言进行端口设计,主要进行以下两个设计。

声明IP和用户6个信号和电源的端口。代码如下:

DC ∶outstd_logic;

RES ∶outstd_logic;

SCLK ∶outstd_logic;

SDIN ∶outstd_logic;

VBAT ∶outstd_logic;

VDD ∶outstd_logic;

将用户端口和IP核端口进行映射,代码如下:

DC =>DC,

RES =>RES,

SCLK =>SCLK,

SDIN =>SDIN,

VBAT =>VBAT,

VDD =>VDD,

(5)在系统生成的user_logIC.v文件中,用Verilog语言进行逻辑设计,实现寄存器和SPI对应端口连接并实时读取,主要代码如下。其中slv_reg0为IP核寄存器,tmp为用户定义临时寄存器,tmp的每一位和IP端口一一对应。实现把slv_reg0寄存器低6位实时传给tmp寄存器,通过对寄存器slv_reg0的写操作达到控制6个引脚的时序。

always@(posedgeBus2IP_Clk)

begin

tmp<=slv_reg0[5:0];

end

4 OLED驱动程序设计

由于ZedBoard开发板上的OLED使用的是SPI协议,并且只支持写,不支持读,因此控制OLED就是在SCLK的时钟下,通过SDIN进行命令和数据的传输。OLED的控制需要经过初始化、传数据和命令以及对显存设置等操作实现。

4.1 初始化

驱动IC的初始化代码,可以参考厂家推荐的设置,但需要根据开发板上OLED实际参数进行一些修改。

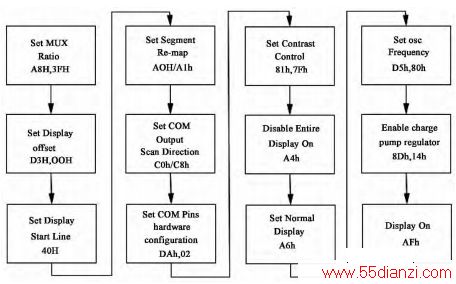

根据SSD1306数据手册的初始化说明,具体步骤如图4所示。初始化的实现就是对SSD1306进行写命令。

图4 SSD1306初始化步骤

4.2 写数据和命令的实现

在SCLK时钟下,根据要写入的数据或者命令,设置SDIN引脚的电平,一位一位地把数据写入SSD1306.SSD1306每次传送的命令和数据均为一个字节,传送数据和命令的区别是通过Set_OLED_DC宏,设置该函数为写数据,通过Clr_OLED_DC宏,设置该函数为写命令。实现一个字节的数据传输代码如下:

for(i=0;i<8;i++)

{

Clr_OLED_SCLK;

if(data&0x80)

Set_OLED_SDIN;

else

Clr_OLED_SDIN;

本文关键字:暂无联系方式显示电路-显示屏,单元电路 - 显示电路-显示屏