4 FPGA设计

在Matlab进行模型仿真的基础上,进一步在FPGA平台上实现数字锁相环。FPGA芯片为XC4VLX100-4,开发环境为 ISE 8.2,综合工具为SynplICity 8.1,仿真工具为ModelSim 6.1b。在XC4VLX100-4芯片上实现后所用资源为slice资源45%,LUTs资源33%。

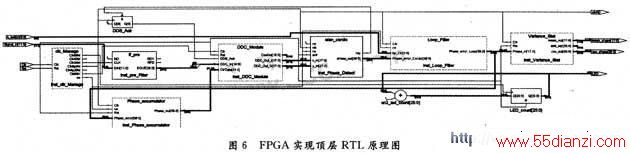

图6为FPGA平台实现后顶层RTL原理图。

5结 语

深空测距 中因其输入信号微弱,具有多普勒频偏等特点,这就要求锁相环带宽在一定范围可变的前提下尽量压窄。本文首先介绍数字锁相环结构为建立Matlab模型打下基础,再通过公式计算与模型仿真得到带宽低至0.1 Hz环路的系数,同时为克服 超窄带锁相环 锁定时间长的缺陷,设计 可变带宽 环路以加快锁定速度,最后通过仿真验证。

在实际设计中,整个环路主要考虑实现超窄以提高对弱测距信号提取能力,故变带宽范围比较有限。为应付更大范围多普勒频偏,需要外部电路对NCO进行频率引导或添加锁频环电路。