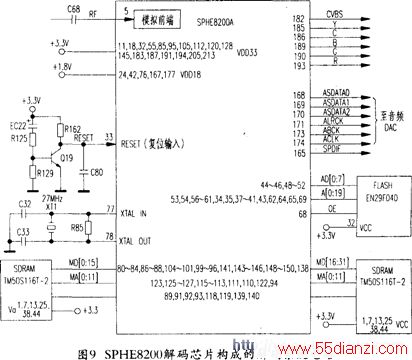

SPHE8200解码芯片构成的解码系统

1、SPHE8200解码芯片简介

SPHE8200是台湾省凌阳公司采用高集成技术,将数字信号处理、数字伺服处理、解码与视频编码及嵌入式CPU融为一体的、功能更为强人的整合型DVD多解码芯片,支持MPEG1和MPEG2音视频解码、支持AC-3和DTS编码格式解码。该芯片采用+3.3V和+1.8V两组供电方式,其封装采用218脚J?QFP~眵式。

2.SPHE8200解码芯片构成的解码系统电路分析

采用以SPHE8200解码芯片为核心,配置装有软件的FLASH(EN29F040)和两块16MB SDRAMf'FM50Sl 16T1构成一个32MB空间的MPE(;2主类主级解码系统,其组成电路如图9所示。可将播放CD格式输人的位流与播放DVD格式输入的位流按不同的解压算法进行MPEGl/MPE(:2解码。直接输出视频信号、音频数据与数字音频信号。

接通市电。开关电源便向构成解码系统的芯片SP[{E8200、EN29F'040、‘rM50S116T和复位电路等各供电端提供稳定的3.3V和+1.8V直流工作电压f见图9)。其中+1.8V通过抗扰滤波电路,向SP[{E8200的VDDl8供电端⑩、⑧、⑩、⑩、⑩脚供电。其中3.3V通过抗扰滤波电路,向sPHE8200的vD【)33供电端⑨、⑩、③、⑦、⑤、⑧、⑩、①、⑩、⑩、⑩、@、⑩、⑨、⑨、⑩、④脚供电;+3.3V还向TM50S116T的VCC供电端①、⑦、⑩、⑤、⑧、⑩脚和EN29F040的VCC供电端⑩脚供电;同时还向由Q19、E(;22、R125、R129、R162等构成的复位电路供电,数十毫秒后,便从Q19集电极输出・个正跳变的复位脉冲信号RESET,从④脚送人解码芯片SPHE8200的复位端fRESET),嵌入式CPU首先被复位自身初始化,确认⑥和④脚的27Ml{z时钟正常后,SPHE8200便通过8位数据线、20位地址 线和控制线从EN29F040中读取初始化程序。再通过数据通讯电路对各受控电路实施初始化操作,同时还将解码程序与控制程序下载存入TM50S116T下载程序的缓冲区。作为执行程序。则该解码系统电路进入正常工作状态。

嵌入在SPHE8200芯片内的CPU,在获得播放碟片类别信息之后,能依据其压缩格式,控制音/视频解码器自动进入相应MPEG-1或MPEG-2音/视频解压运算模式。在解码过程中读取其视频和音频PES头缓冲器中的系统头数据进行缓冲读/写、片选/中断与存储区域分配等操作。

在播放期间,由SPHE8200对从内置通道解码单元输入的码流进行解复用处理,提取视频/音频PES数据和专用数据等,然后通过16位数据线和12位地址线存入TM50S116T分配的缓冲区,以备解码用。

视频解码器与视频处理单元同时从TM50S116T分配的缓冲区读取其数据。前者自动读取PES缓冲区中的视频数据进行解码,并将处理后的数据存入TM50S116T分配的解码图像数据缓冲区。以备视频处理单元用;后者在嵌入式微控器的控制下,视其情况自动读取分散存储在TM50S116T中的一帧亮度数据和色度数据,进行(逐行或隔行)图像帧重建的图像数据送视频输出电路。

视频输出电路,还把子图像解码的字幕等数据嵌入图像数据帧中。

连续输出(逐行或隔行)扫描格式的图像数据送内置的视频编码器。分别处理成亮度数据Y和色度数据C、复合视频数据V和RGB数据:这些数据经6个10 bit的DAC转换成模拟的视频信号,分别从SPHE8200的182脚输出模拟视频信号(CVBS)、185脚输出模拟亮度信号Y、186脚输出模拟色度信号C、189脚输出B信号、190脚输出G信号、193脚输出R信号。

音频解码器自动从TM50S116T读出缓冲区中的音频PES数据,并对播放VCD或DVD碟片的音频位流分别进行MPEG-1或MPEG-2解码音频帧,对播放具有AC-3、DTS、HDCD和DVD-Audio方式编码的碟片,在专用指令程序控制下进行解码。并由音频输出单元处理成立体声音频串行数据(ASDATA0)或环绕声(5.1)音频串行数据fASDATA0~ASDA-TA2)。分别从SPHE8200的168脚输出ASDATA0音频串行数据、169脚输出ASDATA1音频串行数据、170脚输出ASDATA2音频串行数据:还分别从SPHE8200的173脚输出ABCK时钟信号、171脚输出ALRCK时钟信号、174脚输出ACLK时钟信号提供给音频DAC电路。其数字音频(SPDIF)信号从165脚输出。

本文关键字:暂无联系方式编、解码-加、解密电路,单元电路 - 编、解码-加、解密电路