一款基于S3C2440A的银行评价器的设计

点击数:7312 次 录入时间:03-04 11:38:45 整理:http://www.55dianzi.com 嵌入式系统-技术

www.55dianzi.com

以上都是针对微处理器S3C2440A要做的一些软件开发,但嵌入式系统是一个实时操作性很强的东西,尤其是在某些具体产品设计上,容易出现一些问题。而这些问题的根源,往往出现在时序问题上。基于这样的考虑,嵌入式系统往往就要引入CPLD来协调微处理器与其他外围电路或设备的时序问题。

3.2 XL95144XL的软件开发

XL95144XL是一款使用非常广泛的CPLD。CPLD的编程语言主要有两种:VHDL和Verilog HDL语言。在这里,采用VHDL语言来实现对XL9514 4XL编程。VHDL语言是一种描述、模拟、综合、优化和布线的标准硬件描述语言,具有很强的移植能力,它可以从一个模拟器移植到另一个模拟器上、从一个综合器移植到另一个综合器上或者从一个工作平台移植到另一个工作平台上去执行。

在这个银行评价器软件中,CPLD实现的功能主要有两个:一个是外围设备的地址分配功能,实现外围设备与S3C2440A之间的正确地址连接;第二个就是协调时序或同步信号,使得相关的外围设备能够正常工作。XL95144XL实现这两个功能非常容易方便,程序量虽然不大,但起到的作用很大。

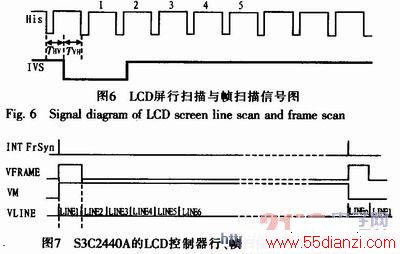

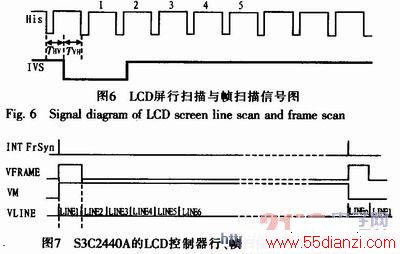

例如,选用一款TFT型LCD液晶屏进行图像显示,该款屏对于行扫描信号与帧扫描的时序要求很严格,如图6所示。如果出现一定时序偏差的话,就容易出现局部“花屏”现象,而微处理器S3C2440A工作后给出的扫描信号的时序并不十分满足液晶屏的指标参数,如图7所示。所以,就需要把扫描信号通过CPLD编程进行协调控制。

从图6、图7可以看出,扫描信号时序不能保证一致性,势必会带来产品设计上的一些缺陷,有的问题甚至会很直观地反映出来,这也就是在嵌入式系统中要加上CPLD的一个重要原因之一了。

3.3 下载和调试

软件编写完成后,就要实现下载。ARM和CPLD都有各自的JTAG下载端口,通过不同的下载线与PC机的通信口进行连接,然后在PC机上使用超级终端分别下载相应的软件包到目标板上运行调试。

4 结论

本文中的银行评价器是基于嵌入式系统开发设计的,它相比于以往的数码管采用数字显示模式的评价器而言,视觉效果有了一个质的飞跃;再者,它也取消了数字按键式的评价方式,采用了触摸屏进行客服评价,起到了更好的效果。与此同时,在不需要进行客服操作的时候,还可以运行其他的一些辅助软件,在一定程度上起到了一个宣传机的作用。由此可见,这样一款基于ARM所设计的银行评价器,功能强大

且易扩展,性能也更好,而且随着电子产业的发展,嵌入式系统的应用越来越广,采用ARM开发设计的评价器来代替传统的数码管式评价器也成为了必然的趋势。

上一页 [1] [2]

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术