O 引 言

脉冲压缩技术是指雷达发射出宽脉冲信号,在接收端,回波宽脉冲信号通过处理后得到窄脉冲的实现过程。它有效地解决了雷达的作用距离和距离分辨力之间的矛盾,可以在不损失雷达威力的前提下提高雷达的距离分辨力,是雷达系统中广泛采用的一种比较成熟的技术。随着数字技术和大规模集成电路技术的飞速发展,采用数字技术实现脉冲压缩越来越显示出优越性。数字脉压在实现滤波的同时,可以方便地实现旁瓣抑制加权处理,既可以有效地缩小脉压系统的设备量,又具有高稳定性和可维护性,进一步提高了系统的可编程性能,是现代脉压系统发展的趋势,特别是高性能DSP(数字信号处理器)的不断推出,为进一步提高数字脉压系统的性能和集成度提供了可能。脉冲压缩信号有多种形式,目前采用最多的是线性调频信号和相位编码信号,本文选用ADI公司的新一代高性能DSP芯片ADSP-TS202,实现线性调频信号的高速、高精度数字脉冲压缩。

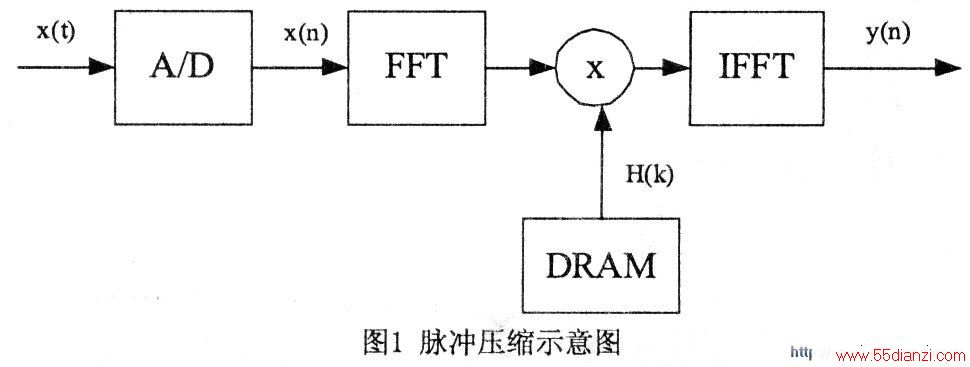

1 脉冲压缩

脉冲压缩器的设计实际上就是匹配滤波器的设计。设发射信号为s(t),根据匹配滤波理论,匹配滤波器的冲击响应为h(t)=s*(t0―t),匹配滤波器输出为y(t)=s(t)*h(t)。数字信号处理时,脉压过程就是通过对回波序列s(n)与匹配滤波器的脉冲响应序列h(n)求线性卷积实现。则数字匹配滤波器的输出:

![]()

式(1)的方法叫做时域相关法。根据傅里叶变换理论,时域卷积等效于频域的乘积,故(1)式可以采用FFT(快速傅立叶变换)和IFFT(快速逆傅立叶变换)在频域实现,这种方法称为频域FFT法。用公式表示为: ![]()

根据匹配滤波理论,FFT[h(n)]=FFT[s*(-n)]=S*(k)。设接收的回波信号为x(t),用频域FFT法实现脉压的具体过程如下:先对接收信号A/D采样后得到x(n),再对信号x(n)进行FFT变换得到X(k),X(k)与发射信号s(t)的采样序列s(n)的FFT的复共轭S*(k)相乘,然后再对乘积作IFFT而获得时域脉压结果。由于S*(k)可以预先算出存入DSP的RAM空间里,每次运算时,只需读出RAM中的数值即可进行运算,在对脉压作加窗处理时,仅需事先将窗函数W(k)与S*(k)的乘积H(k)=S*(k)・W(k)存入RAM中即可,不会额外增加存储量及运算量。脉冲压缩的点数比较大时,频域FFT法的处理速度要比时域相关法快很多,下面讨论用频域FFT法实现高速数字脉冲压缩,文中的脉冲压缩就是基于图1的原理实现的。

2 数字脉压系统的实现

2.1 芯片介绍

ADI公司生产的ADSP-TS202是一款性能极高的静态超标量处理器,具有两个计算块,每计算块均有一个加法器、一个乘法器、一个移位单元,并具有专门的IALU进行地址产生和程序指针管理,每指令周期最多可并行执行四条指令。片上存储空间高达12Mbit,四条相互独立的128 bit宽度的内部数据总线。该处理器可以将多种不同宽度存储单元与双运算模块相结合处理,最高工作频率500MHz。利用其独特的单指令多数据流技术,可以提供40亿次40bitMAc运算或者10亿次80bitMAC运算。

ADSP-TS202内的IALU提供了位反序寻址和循环缓冲寻址等操作,乘法器提供了“定点复数共轭相乘”指令,即当操作数为两个复数a,b时,该指令产生a×b*的结果。利用该指令能使IFFT与FFT共用同一组旋转因子,这样既节省了内存开销,又避免了传统方法中取共轭、排序等耗时的操作;该乘法器还提供了“定点双寄存器乘法”指令,这些特点使得ADSP-TS202特别适用于基于FFT的数字信号处理。

2.2 系统结构和硬件设计

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术

上一篇:基于数学形态学的人脸检测研究