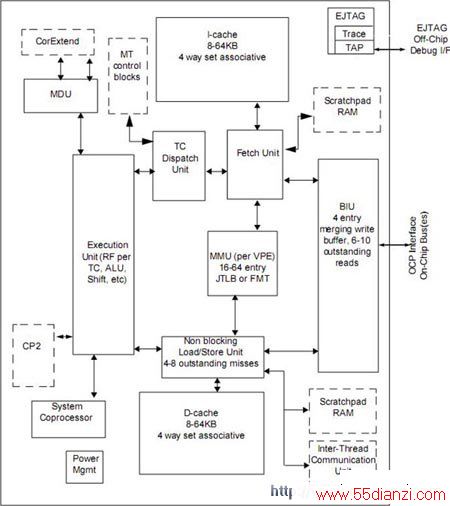

△图说:MIPS 74K处理器结构示意图。

MIPS公司有大产品线,分别是单执行绪的24K与74K系列,以及多执行绪的34K系列。74K甫于今年六月发表,在65nm工艺下,其运作频率已经超越1GHz,采用通用处理器搭配DSP核心的设计,不过总体效能与功耗表现略逊于类似架构的ARM Cortex-A8。多执行绪处理器的主角―34K系列,该处理器核心能设定1或2个虚拟处理组件(VPE)以及最多5个执行绪内容(TC),提供充分的可配置弹性。但是讲白了,其实两个VPE的作法就是将单颗核心模拟为2个核心,使34K核心能同时执行两个独立的操作系统,或是一个双路的对称式多重处理器操作系统。

MIPS32 34Kc核心采用90nm工艺,最差操作状态下频率为500MHz。核心尺寸为2.1mm2,而核心部分耗电量为0.56mW/MHz@1.0V。目前该系列核心共包含34Kc、34Kf、34Kc Pro以及34Kf Pro。这些核心具备完全兼容于IEEE 754规格的硬件浮点运算处理器。其中34Kc Pro与34Kf Pro核心具备CorExtend功能,能让SoC研发业者自行扩增指令。

△图说:MIPS 34K处理器结构示意图。

根据MIPS自家的估算,与同家族的24K系列产品相较起来,34K在2个VPE以及2个TC的组态设定之下,可以将效能提升到超越24K处理器60%的程度,芯片面积大略增加14%,而因为多执行绪作业所导致的高速缓存失误比率则是由4.41%增加到5.16%,算是在可接受的范围之内。

不过与单核心74K相较起来,34K反而更不适用于网络或多媒体串流的密集计算环境,而VPE和TC单元的增加,同样也会加大芯片的面积。虽说MT技术的局限性,使其不适合用于多媒体编译码应用上,但是在汽车电子方面,已经有厂商成功利用2颗34K处理器组成双核多执行绪处理器,并提供的相当优秀的执行效能,有此成功的前例可循,我们也可以预测,未来MIPS将会有更多结合多核与多执行绪的解决方案出现,不过这么一来,在成本调配方面的优势还能剩下多少,就由方案提供厂商去伤脑筋吧。