图3 中断处理应用实例的硬件连接

其中,FIFO采用IDT公司的 IDT72V3650 芯片,FPGA采用ALTERA公司APEX20K系列的EP20K1500E器件。FIFO芯片提供了五个空满状态标志位,可根据不同的实际需求方便的通过FPGA编程向MPC860的IRQ2和IRQ1分别发送开始读信号和停止读信号,从而在时钟的驱动下读取FIFO数据。

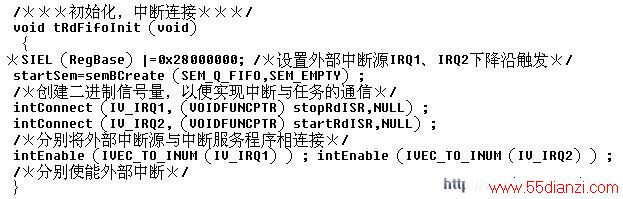

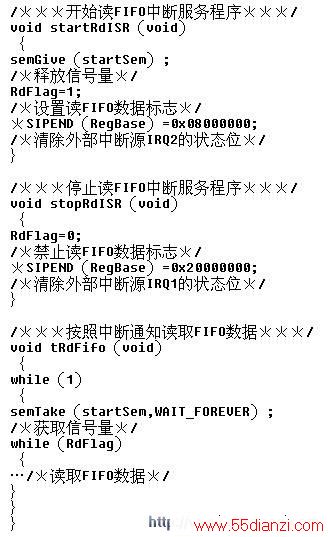

中断应用程序的主要实现函数的代码及注释如下:

点击看原图

6 结束语

嵌入式实时操作系统VxWorks提供的中断处理机制中断延迟小、用户编程方便,被广泛应用于实际工程中。MPC860的中断体系结构是理解如PowerPC系列芯片等双处理器体系结构的中断处理机制的难点。本文在详细分析两者中断处理机制的基础上介绍了具体的开发实例。该实例已在TornadoⅡ 2.0.2版本上调试通过,并成功应用于某型网络设备开发中。

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术