3.3.2 接口

CPLD的主要外围接口如下:(1)输入部分。图像数据lPD[7:0]、时钟LCLK、场同步VREF、行同步HREF、复位RES。(2)输出部分。图像数据IP01[7:0]和IP02[7:O],片选信号eel、ce2,写使能wel、we2,地址addl[18:0]、add2[18:O],总线隔离器的开关信号f1、f2,DSP中断信号dsPINt(这里没有设置SRAM的0E信号,因为CPLD只需要将数据写入SRAM,不需要从SRAM中读数据)。

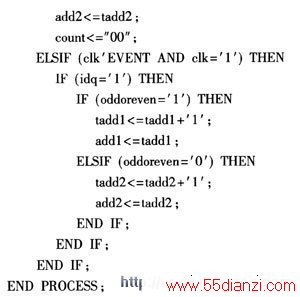

3.3.3 VHDL实现

设计中采用VHDL对CPLD进行逻辑实现。程序中“乒乓”控制部分代码如下:

本文设计了一套基于 视频 解码 芯片SAA7114H与CPLD的实时 图像采集 系统,其硬件结构简单,系统稳定,完全满足基于DSP的活动目标跟踪系统的需要,具有很强的实用性,稍加改动即可用于其他场合,如监控系统等。

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术