内容摘要:介绍了FPGA内嵌的PCI Express硬核端点模块和Wishbone片上总线规范。应用VHDL语言,编程实现了Wishbone总线的主从端口,以及TLP包的编码和解码功能。在FPGA上运行程序并使用Chipscope测试时序波形,验证了接口数据传输的稳定性和正确性。

关键词:PCI Express总线;FPGA;PCIE端点模块;Wishbone

引言

当前,基于FPGA实现PCI Express接口有两种方案,一是采用第三方PHY接口器件和FPGA实现;二是采用集成GTP的FPGA来实现。集成GTP的FPGA实现PCI Express接口在链路效率、兼容性测试及资源可用性等方面有其独特的优势。随着技术的发展和对传输数据速率和灵活性要求的提高,将更加趋于利用高性能FPGA(即集成GTP的FPGA)来实现PCIExpress接口功能。但是,要在FPGA上实现PCI Express通信桥接,还需要用户根据PCI Express协议构建自己的软IP或者向第三方或FPGA供应商购买IP核。构建IP核的难题在于其难度较大且开发周期较长;向第三方或FPGA供应商购买的IP,存在专利费用问题。对于一些验证性开发,其重点一般在于应用功能的实现,而希望公共模块(如PCI Express接口)的开发在满足性能的前提下,尽量少花时间和费用,从而缩短开发周期和成本。因此,利用已有可获取资源,实现PCI Express接口成为这类开发中的首选。

Xilinx的V5/V6系列FPGA芯片中已集成了硬核端点的PCI Express模块,提供了PCI Express接口的底层配置,相当于提供了一个专用协议与PCI Express之间的桥梁。在PCI Express硬核端点上集成片上总线,实现PCI Express与应用模块互联,将能更快地实现PCI Express接口的开发。

目前比较常见的片上总线规范有IBM公司的CoreConnect,ARM公司的AMBA和SILICore Corp公司的Wishbone。CoreConnect和AMBA规范复杂,在设计中需要建立连接桥以连接不同IP核。相对于其他两种接口规范,Wishbone接口规范具有简单、高效、易于实现等特点,而且完全免费。因此,本文采用Wishbone总线规范实现PCI Exprpess接口。

1 Wishbone基本原理、Xilinx集成端点IP及TLP包结构

1.1 Wishhone的基本原理

Wishbone最先是由Silicore公司提出的,现在己被移交给OpenCores组织维护。其开放性、简单性和灵活性受到广大设计者的青睐,现在己有不少的用户群体,特别是一些免费的IP核,采用Wishbone标准。除了具备地址/数据总线宽度可变、互联结构可变及仲裁机制灵活等片上总线的共同特点外,Wishhone还包括以下特征:

(1)支持点到点、共享总线、十字交叉和基于交换结构的互联;

(2)支持常用的总线数据传输协议,如单字节读写周期、块传输周期、控制操作及其他的总线事务等;

(3)主/从结构,支持多控制器和64位地址空间,从端部分地址解码;握手协议使得每个核都可以控制数据的传输速度;

(4)用户自定义标记(TAG),确定数据传输类型、中断向量等;

(5)接口简单、紧凑,总线实现的逻辑单元少。

Wishhone采用主端(Master)和从端(Slave)的架构。主端模块发出数据传送请求,然后通过一个接口网络和从端进行数据交换,其系统结构如图1所示。这个接口网络称之为INTERCON,各终端之间访问通过INTERCON,INTERCON内部可根据访问情况采用不同的互连方式,Wishbone将它称为可变互联网络。可变互联网络的连接形式有点对点、数据流、共享总线和交叉总线等。

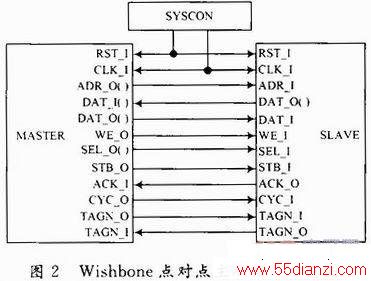

Wishbone可变的互连方式允许系统设计工程师可以采用不同的IP核互连方式,以满足不同场合的要求。根据需要,本设计采用点对点的总线互连方式。图2给出了点对点的MASTER/SLAVE主从接口图。其中SYSCON为产生时钟和复位信号,TAGN为用户自定义信号。

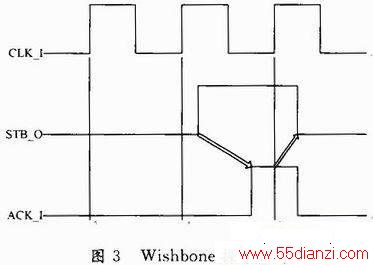

Wishbone数据传输的握手机制如图3所示。准备传输数据时,Master设置STB_O输出信号为有效(Wishbone设置高电平为有效电平),表示开始对Slave进行访问;当接收完数据,Master的ACK_I信号接收到Slave发出的完成信号,然后Master取消STB_O信号。Slave可以置RTY_O为高,表示Slave现在忙,以后再试;还可以置ERR_O为高,表示出错。在Master和Slave传输数据期间,两端都可以控制数据的传输速度。

1.2 Xilinx集成硬核端点IP结构

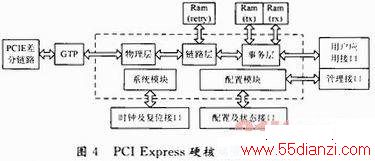

Xilinx的端点IP符合PCIe协议V1.1,集成了PCI Express协议中的物理层(PHY)、数据链接层(DLL)和传输层(TLL),其结构框图如图4所示,包含有以下几个接口:时钟及复位接口;事务层接口;管理接口;缓存接口;收发器接口;配置和状态接口。

事务层接口,与用户应用设计连接。在本次设计中连接到Wishbone从接口。

时钟及复位接口,包含DCM所需的反馈时钟。在本次设计中系统参考时钟为100 MHz,用户时钟为62.5MHz。

收发器接口,与GTP相连。包含多条发送和接收链路,每条链路包含一对发送和一对接收信号,发送和接收信号都是差分信号,本文采用X1。

缓存接口,与事务层和数据链路层相连。用来实现数据传输的缓冲。这三个缓存器已在CORE Generator中进行了例化和配置。BLOCk RAM数据通路为64位宽。三个Block RAM接口均与端点模块的其余部分同步运行。每个接口都具备单独的读写地址、数据和控制信号。

管理接口,用于访问端点模块中的各种寄存器和信号,包括PCI Express配置空间、各种控制和状态寄存器。管理接口还包含用于统计数据和监测的输出信号以及一个读取流量控制信用输出的接口。

配置及状态接口包含控制和状态、错误、后端接口配置以及中断端口。

收发器接口、存储器接口以及时钟和复位接口在CORE Generator封装中自动连接。这些接口在封装之外均不可见。

1.3 TLP包结构

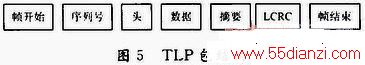

PCI Express协议是基于TLP包传输的,在PCIExpress设备之间传输的TLP结构如图5所示。数据发送时,来自软件层/核心设备的核心信息包括头以及数据部分(某些TLP不包含数据),经事务层添加摘要部分,发往数据链路层后附加序列号及LCRC,最后在物理层添加帧开始及结束标志后发送;数据接收时,逐层去掉附加部分,最后将头及数据部分送至软件层/核心设备。

在每个头中含有类型及格式两个字段,它们定义头剩余部分的格式,用来指定事务的类型、头的大小、数据有效载荷是否存在等。事务(在PCI Express请求者和完成者之间进行的操作)包括存储器事务、I/O事务、配置事务和消息事务。事务分为三个类别:posted(不需要响应,不需要返回完成包,存储器写和消息属于此类事务),非posted(需要响应)和完成包。

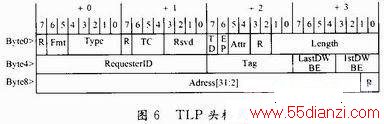

本文设计的基于Wishbone的PCI Express接口的读写操作针对存储器空间,其中存储器读写操作TLP头的格式如图6所示。类型字段(FMt)为00000b时表示存储器读或者写;格式字段(Type)为00/01b时表示3DW/4DW的存储器读操作,为10/11b时表示3DW/4DW的存储器写操作。

2 基于Wishboen的PCI Express接口实现

2.1 实现原理

本文基于Xilinx FPGA的PCI Express集成硬核端点模块和Wishhone片上总线,实现了主机和外接存储器问通过PCI Express的接口通信。PCI Express接口基于协议包传输机制,因此,集成端点模块的数据传输均以TLP包的形式进行。实现数据传输可通过以下步骤进行(以PCI Express读传输为例):

(1)待传输数据存储在应用模块中的数据缓存器中,数据缓存器可以使用片外存储器也可以使用片内RAM资源。本设计使用的是片内RAM资源;

本文关键字:暂无联系方式嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术