前言

目前的高端ASIC/ASSP/SoC器件开发商可考虑分为三大类:主流、早期采用者和技术领导者。在写这篇文章的时候,主流开发商正致力于65纳米技术节点设计,早期采用者开发商正专注于45/40纳米节点设计,而技术领导者开发商正力求超越32/28纳米及更小尺寸节点设计。随着技术采用开发步伐的日益加快,下一代的早期采用者过渡到32/28纳米节点的时间将不会很久,而他们的主流开发商同行也将紧随其后。

进行32/28纳米节点设计时会遇到许许多多的问题,包括:低功耗设计、串扰效应、工艺变异及操作模式和角点数量的显著增加。本文首先会为您呈现微捷码Talus® Vortex 1.2物理实现流程的高层次视图,接着将介绍32/28纳米节点设计所包含的一些问题并描述Talus Vortex 1.2是如何解决的这些问题。

除了上述技术问题以外,32/28纳米节点日益提高的设计规模和复杂性还造成了工程资源(在不扩大团队规模的前提下取得更大成果,同时还保持甚至缩短现有时间表)、硬件资源(无须增加内存或购买全新设备,利用现有设备和服务器处理更大型设计)、满足日益紧张的开发时间表等方面相关问题的增加。为了解决这些问题,本文还将描述通过Talus Vortex FX创新性的Distributed Smart Sync™(分布式智能同步)技术, Talus Vortex显著地提高了其容量和性能。Talus Vortex FX 提供了首款且唯一一款分布式布局布线解决方案。

Talus Vortex 1.2物理实现流程介绍

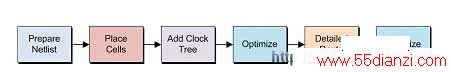

图1所展示的是标准Talus Vortex 1.2物理流程的高层次视图。从图中,您不难观察到它先假设了芯片级网表的存在,此网表可能已通过微捷码或第三方的设计输入和综合工具而生成。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术