����SRAM�и��ٺͲ���ˢ�µ��ŵ㣬���㷺���ڸ����ܵļ����ϵͳ�����ڰ뵼�幤�ռ���������Լ��洢ϵͳ������Ҫ���洢������������١����ɷ���չ����ʹϵͳ����ǿ���ͬʱ��Ҳ������ϵͳ�ĸ����ԣ�����·�Ĺ�����ϴ����˲�С������[12]�����ڴ洢�����ܺͽṹ�ĸ����ԣ������Ϊ����ȷ�ش������ݺ������������û��ij����뱣֤SRAM��Ԫ��Ѱַ��ȡָ���Լ�������ȷ���Գ�������ݴ洢��Ԫ����ȷ�����Ǻ���Ҫ�ķ��棬��˱�֤�洢�����������ȶ�������ϵͳ�ȶ�������ǰ�ᡣ������Ҫ��ͨ���Գ�����SRAM��������ķ���������March C�㷨����FPGA�����ɵ�SRAM�Լ���Ե�·��SRAMϵͳ���й��ϼ��������

����

1������ģ�� ������ν����ģ�ͣ���ָΪ���о����϶Ե�·��ϵͳ��Ӱ�죬���(��λ)���ϵ�λ�ã��Թ�����һЩ���ಢѡ��������ϵĹ��̡�SRAMϵͳ�ɳ���Ϊһ�黥���Ĺ���ģ��,�����ڸ���ģ����ɷ�����Van de Goor����[3]�����Ϊ��ַ����������д�����洢����Ԫ����3����,��֤��ǰ��������ߵĹ����ڹ������ǵȼ۵�,����ֻ��Ҫ���洢��Ԫ���й��ϡ�������SRAM����ģ����Ҫ��Ϊ���¼�������[4]��

�� �̶����ϣ�Stuck��At Faults, SAF���������е�һ��������Ԫ��һλ���λ�̶�Ϊ0��̶�Ϊ1��

�� ��·����(Open Faults, OF)�������е�һ��������Ԫ��·��0��·��1��

�� ��Ϲ���(Coupling Faults, CF)���洢��Ԫ��ijЩλ�����䵼������λ����ֵ������Ԥ�ڵı仯���ȿ��Է����ڲ�ͬ��Ԫ֮�䡣Ҳ���Է�����ͬһ��Ԫ�IJ�ͬλ֮�䡣��������������ͬ��Ԫ֮�����Ϲ��ϼ�Ϊ��һ����Ϲ��ϣ���������ͬһ��Ԫ��ͬλ֮�����Ϲ��ϼ�Ϊ�ڶ�����Ϲ��ϡ�

������һ����Ϲ����ֿɷ�Ϊ��ת��Ϲ��ϡ��ݵ���Ϲ����Լ�״̬��Ϲ��ϵȡ���ת��Ϲ����Ǵ洢��Ci��Ԫ������ϵ�Ԫ���е�����������ϵ�ԪCj�е���ֵ������ת�Ĺ��ϡ�����“��”��ʾ��ֵ��0→1�������䣬��“ ��”��ʾ��ֵ��1→0�������䣬����“ ��”��ʾ��ֵ�ķ�ת����������Ͽ�����Ϊ<�ѣ���>��<�ԣ���>���ݵ���Ϲ�����ָ��Ci�е�ֵ����ʱ��Cj�е�ֵ�̶�Ϊ0��1��������Ϊ<��;0>��<�ѣ�1>��<�ԣ�0>��<�ԣ�1>[5]����״̬��Ϲ�����������ϵ�Ԫ����һ�ض�״̬ʱ������ϵ�Ԫ���ȴ���0��1����<0��0>��<0��1>��<1��0>��<1��1>״̬��

�����ڶ�����Ϲ��ϼ�ͬһ��Ԫ��ͬλ������Ҳ�����Ƶ����������д�źź�ǿʱ��ͬһ��Ԫ��ͬλ�����ϾͿ��ܱ���û��ֻ���ֳ�д�����Ϣ��

�� ������ϣ�Transition Faults,TF���������е�һ��������Ԫ��һλ���λ����Ԥ�ڵ�ʱ����������ݴ�0��1���1��0�����䣬��Ϊ<��;0>��<��;1>�����ֹ��Ͽ��ƿɹ�Ϊ�̶����ϣ�ʵ����������ͬ������״̬�����κ�ʱ�̶������䣬���з�ת��Ϲ���Ӱ����ʱ�ͻ����ԭ��������ɵ����䡣

�� �ɵ�ַ�����������ĵ�Ԫ���й��ϣ�Address Decoder Fault��AF����������ij��ַ���ܷ����κε�Ԫ��ij��Ԫ���ܱ��κε�ַ���ʡ�ij����ַ���Է��ʶ����Ԫ��ij����Ԫ�ɱ������ַ���ʡ�

����

2��SRAM���Է��� ����SRAM�IJ��Է�����Ҫ������3�֡�

(1) ֱ�Ӵ�ȡ����

����ֱ�Ӵ�ȡ�����Dz���һ�ֲ��Խṹ��������SRAM���е�ֱ�ӷ��ʡ���ͨ�������Զ������豸���в��ԣ����Դӷ�װ����ֱ�Ӷ�Ƕ��ʽ�洢�����з��ʣ����߿��Դӷ�װ���ŶԲ���״̬���Լ���һЩΪ�洢���ṩ���ݵ���ˮ�߽ṹ�еĴ���״̬���з���,�ܹ�����ʵ�ֶ��ָ����������㷨����ȱ���ǣ���ATE����ʵ�ֵ��㷨Խ���ӣ���ATE���洢��������Ҫ��Խ�ߣ���ATE���ϲ���ʵ�ֶ�Ƕ��ʽ�洢����“ȫ��”���ԣ�����ʱ�ӵĹ���Ƶ��Խ�ߣ����Գɱ�Խ�ߣ�����оƬ��Χ���ŵ����ƣ���оƬ�ڴ�����SRAM����ֱ�Ӳ�������������ʵ��

(2) ����Ƕ������������Ӳ��Դ洢��

���������ֲ��Է����У�ͨ��Ƕ��ʽ�������Դ洢�����ж�/д����������������һϵ���������ij�����롣��Щ������Է��ڳ���洢����,��Ƕ��ʽоƬ�ӿڴ�ʩ�Ӵ��룬���Դ洢���Ĺ��̾���������ִ�в��Գ���Ĺ��̡����ŵ��Dz���Ҫ��Ӳ��������κ���,���Ҳ����㷨������ʵ�ֿ���ͨ�����������������������ɡ�

(3) �洢���ڽ��Բ���(MBIST)

�����洢���ڽ��Բ��Լ�����Memory BuildIn Self Test, MBIST���Ĺ���ԭ�����ڴ洢����Χ����һ�����Ƶ�·���������ݷ�������ַ���������Ʋ����Լ�����Ƚϵȵ�·��ʵ��оƬ���ô洢������ģʽ���Զ������Լ����Խ�����Զ��б�оƬ�ⲿ�Ŀ��ƿ�����оƬ�Զ������ڲ��洢������ģʽ��MBIST���������Զ������ڲ�����ģʽ������Ҳ����ʵ�ֲ��в��ԡ�������Ҫ���Ӷ��������·������MBIST������ȱ������������оƬ��������п���Ӱ��оƬ��ʱ�����ԡ����ڲ�ͬ�����Ĵ洢����MBIST��·�Ĺ�ģ������ͬ����ˣ����Ŵ洢�����������ӣ����ַ��������ӵ�оƬ�����ռ�ı�����Խ�С���������ֲ��Լ������кܶ������������ơ�

���������о����Ǽ�����ڵ�SRAM���Է��������ڴ���SRAMλ�ڼ����ϵͳ�ڲ����Ǹ�ϵͳ�Ĺؼ����֣���˱��IJ���FPGA��Ϊ�����ϵͳ��SRAM֮��ͨ�ŵ�������ͨ�����ռ���������Ŀ����źţ��Զ�����һ��SRAM�Բ��Ե�·��

����

3��March C�㷨 ������Դ洢���еĸ��ֹ���ģ�Ϳ����˶��ִ洢�������㷨����March�㷨��Walking�㷨��GalloPINg�㷨�ȡ�����March�㷨�ǽϼIJ����㷨֮һ�����нϸߵĹ��ϸ����ʺͽ�С��ʱ�临�Ӷȣ�����March�㷨����õĴ洢�������㷨�����㷨������θĽ��������˺ܶ���֣���MATS��MATS+��March X��March C��March C���㷨[6]��

����March C�㷨����MarchԪ�ع��ɵ����У������ԭ������������״̬����������ÿһ����ַ���ж�/д0��1��������֤ÿ�����ֽ�֮��IJ��������00��01��10��11������������ٸ�һ�Σ�����Ϊ�˼��ߵ͵�ַ��/д˳����ϣ��ֱ���е�ַ�����͵�ַ�ݼ����ֲ�����ͨ���Դ洢�����ϵض�д���ܹ���⼸�����еĴ洢�����ϡ�

����������March C�㷨�У��ۺϿ����㷨�Ĺ��ϸ����ʼ����Գɱ������أ�����ѡ���ܹ���Ч��������洢�����ϵ�March C�㷨��March C�㷨�ľ�����������[7]:

�������У�“��”��ʾ��ַ������“��”��ʾ��ַ�Ľ���“ ��”��ʾ����˳���ԣ�r0��w0��r1��w1�ֱ��ʾ��0��д0����1��д1��M0��M5�ֱ��ʾһ��March��Ԫ��March C�㷨�ܹ���Ч���� SAF��TF��CF��AF�ȹ��ϡ����У�SAF���Ͽ��� M0��M1��Ԫ�� M1��M2��Ԫ������TF������0→1���Ͽ���M3��M4��Ԫ������1→0���Ͽ���M2��M3��Ԫ��������CF�����У�1→0���Ͽ���M2��M3��Ԫ��M4��M5��Ԫ������0→1���Ͽ���M1��M2��Ԫ��M3��M4��Ԫ��������1���Ͽ���M2��M3��Ԫ��M4��M5��Ԫ��������0���Ͽ���M1��M2��Ԫ��M2��M3��Ԫ������AF���Ͽ�����March��Ԫ����������/�����еõ���⡣

www.55dianzi.com

����4��SRAM�Բ��Ե�·��ʵ��

����SRAM�Բ��Ե�·��Ϊ�˼��洢���ĺû���������洢��Ԫ����������Լ�ġ������Բ��Ե�·����FPGA���ɣ�ͨ����Ӧ�����ϵͳ�Ŀ����źţ��������һ���������Լ���Ե�·��

���� 4.1��Ӳ����������

�������Ե�·�IJ�������ͨ��Ӳ����������Verilog���ʵ�֡���Verilog�����е�·��ƣ�����߿��Խ��и��ּ��������ƣ��Լ�������ϵͳ�ķ�����֤��ʱ����������ۺϡ�����ĿǰӦ����㷺��һ��Ӳ���������ԡ�

��������Ӳ���������Խ������ʱ������Ӳ���������Եı��������Ժ����ذ���ɵ������ֲ����ͬ���ҵIJ�ͬоƬ��ȥ�����ڲ�ͬ��ģӦ��ʱ���������ġ������ź�λ���Ǻ����ı�ģ����Ժ����ض��������ģ�����Ӧ��ͬ��ģ��Ӧ�á��ڷ�����֤ʱ���������ʸ����������ͬһ��������������ɣ���Ϊ����Ӳ�����������ۺ������ɵ���������һ�ֱ��ĵ�����ƻ�����ʽ(EDIF)�ļ��������������õ�ʵ�ֹ��ա��йع��ղ�������������ͨ��Ӳ�����������ṩ�����Ա��Ȼ�����ò�ͬ���ҵIJ��ֲ��߹��ߣ��ڲ�ͬ���յ�оƬ��ʵ�֡�

���� 4.2��ϵͳӲ��

���������ϵͳ�����ж����Χ�豸���ڱ�ϵͳ�м������SRAM֮���ͨ��ͨ��FPGA�����ݣ��������FPGA�IJ���Ҳ���Ƕ�SRAM�IJ�����ϵͳӲ����·�ṹ��ͼ��ͼ1��ʾ��

ͼ1��ϵͳӲ����·�ṹ��ͼ

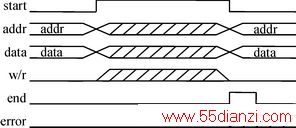

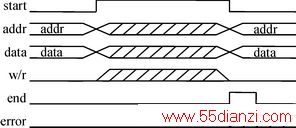

����ͼ�е�start�ź����Dz��������źţ���������Ч��end�ź����Dz��Խ����ź��ߣ���������Ч��error��SRAM�����źţ��ߵ�ƽ��Ч��addrΪ��ַ���ߣ�dataΪ�������ߣ�r/wΪ��/д�ź��ߡ�ϵͳʱ��ͼ��ͼ2��ʾ��������Ӱ����Ϊδ֪����

ͼ2��ϵͳʱ��ͼ

[1] [2] ��һҳ

���Ĺؼ��֣��洢�� ��� DSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����