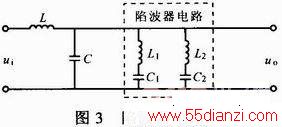

(2)陷波器的设计

为进一步降低谐波失真,在输出滤波器后侧设置了两级陷波器电路,电路如图3所示。

图中,L1与C1构成第一级陷波器,用于滤除开关频率噪声,谐振频率取fs(80 kHz),取C1=2μF,则L1=[1/(2πfs)2]/C1=2μH;L2与C2构成第二级陷波器,滤除开关频率二倍频噪声。谐振频率取为160 kHz,取C2=2μF,则L2=500 nH。

4 实验结果

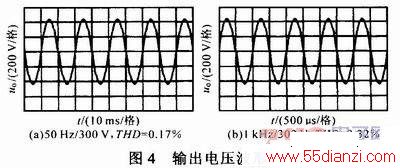

在样机上进行了实验验证。额定输出功率750 VA,可实现频率变化范围45 Hz~1 kHz,频率分辨率为10 μHz,电压变化范围0~300 V。满载300 V正弦电压输出波形uo如图4所示。

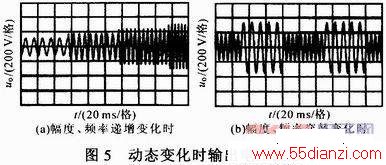

图5示出动态变化时uo波形。图5a中uo由100 Hz/80 V逐渐向250 Hz/200 V变化,图5b中uo在100Hz/240 V和200 Hz/120 V之间交替变化。

5 结论

实验结果表明,该方案较好地实现了复杂测试对交流电源的需求。采用先进的DDS技术,实现输出精度高、波形输出灵活等性能,利用EDA方法,将实现任意波形的DDS关键核心部分集成在FPGA芯片内,大大简化了电路,降低了成本,提高了可靠性。采用正弦调制技术,实现了输出功率大、谐波含量低等性能。通过实际测试,取得了比较理想的效果,完全符合设计要求。

上一篇:基于CPLD加载FPGA的方案